2D晶体管的未来展望

作者:admin 来源:半导体行业观察 发布时间:2023-11-06 访问量:2537

学术界和工业界已经提出将二维(2D)过渡金属二掺杂化合物(TMD)半导体作为未来取代物理栅极长度小于10纳米的硅晶体管的一种选择。在这篇评论中,我们分享了基于堆叠二维TMD纳米带制造互补金属氧化物半导体 (CMOS) 器件的最新进展,并特别强调了二维界在五个关键研究领域仍需解决的问题:接触、沟道生长、栅极氧化物、可变性和掺杂。虽然二维TMD晶体管具有巨大的潜力,但还需要更多的研究来了解二维材料在原子尺度上的物理相互作用。

学术界和工业界已经提出了二维TMD半导体(如MoS2、WSe2等)作为硅(Si)晶体管的潜在替代品,其物理栅极长度为10纳米以下,采用全栅极(GAA)堆叠纳米带(NR)1,2,3,4。GAA NR的静电特性决定了当物理栅极长度缩小到10纳米以下时,半导体沟道的厚度必须大大降低到5纳米以下,才能保持低于70 mV/dec 的亚阈值摆幅 (SS),从而有效地关闭晶体管。如果没有较低的SS,晶体管要么会在关断状态泄漏过多电流,要么需要更高的电压才能工作。

我们在图 1 中使用密度泛函理论 (DFT) 原子模拟对各种器件几何形状的二维纳米片计算出的 SS 进行了比较,从而说明了这一点。在栅极长度小于 10 nm 的情况下,源极和漏极之间的直接隧穿预计会导致硅晶体管和其他传统体晶体管的高离态漏电。TMD 的大带隙及其高有效质量抑制了源极和漏极之间的直接隧穿,从而使关态电流保持在较低水平。此外,硅的迁移率会随着沟道厚度的减小而降低,而二维 TMD 的迁移率却能保持不变5。这为二维 TMD 晶体管在 10 纳米以下物理栅极长度或 1 纳米以下节点取代硅提供了机会。

然而,向新半导体材料过渡的实际可行性和时间安排仍是一个悬而未决的问题。在取代硅之前,二维界需要解决许多难题。在这篇评论中,我们将阐述二维 TMD 的一些有前途的特性,并强调目前阻碍半导体行业采用这些材料的问题。

图 1:各种晶体管几何形状的阈下摆幅 (SS) 与沟道长度的比较,说明二维纳米片的优势。

半导体几何形状(平面、FinFET、纳米带和二维纳米片)的SS与Leff(栅极长度)的模拟显示,在物理栅极长度小于10 nm时,二维过渡金属二钙化物的静电与硅相比具有竞争性。二维纳米片SS是通过原子密度泛函理论计算得出的,而其他几何形状则是通过静电求解得出的。

半导体器件的未来将以堆叠GAA NR结构为中心,与硅GAA NR相比,二维TMD具有独特的扩展优势。图2显示了堆叠硅 GAA NR 和堆叠二维TMD GAA NR晶体管在同等高度上的横截面,以考虑到常见的工艺集成因素,包括蚀刻晶体管堆叠所面临的挑战。二维TMD GAA NR结构的优势显而易见,因为在相同的体积内可以放置更多的二维TMD NR。具体来说,相同的栅极高度可以容纳6个2D TMD NR,而Si NR只有4个。这样,即使单个TMD纳米片的性能低于单个硅纳米片,相同尺寸的 2D TMD GAA NR 晶体管也能达到比硅更高的性能。

图 2:具有相同物理高度的堆叠纳米带晶体管示意图。

物理高度相同的叠层全栅极 (GAA) 硅晶体管与叠层 GAA 二维 TMD 纳米带 (NR) 晶体管的截面图对比。假设栅极氧化物和栅极金属沉积体积相同,则四个堆叠硅 NR 的高度与六个堆叠二维 TMD NR 的高度相同。因此,二维 TMD 驱动电流只需达到硅驱动电流的 2/3,就具有竞争力。b.面板显示的是相同的图纸,但以二维 TMD 薄膜的单个原子为比例。金属触点用灰色表示,间隔电介质用黄色表示,栅极氧化物用粉红色表示。栅极金属未显示。“Advancing 2D monolayer CMOS through contact, channel and interface engineering,” 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2021, pp. 7.1.1–7.1.4, https://doi.org/10.1109/IEDM19574.2021.9720651.

制造二维 TMD 晶体管面临的挑战

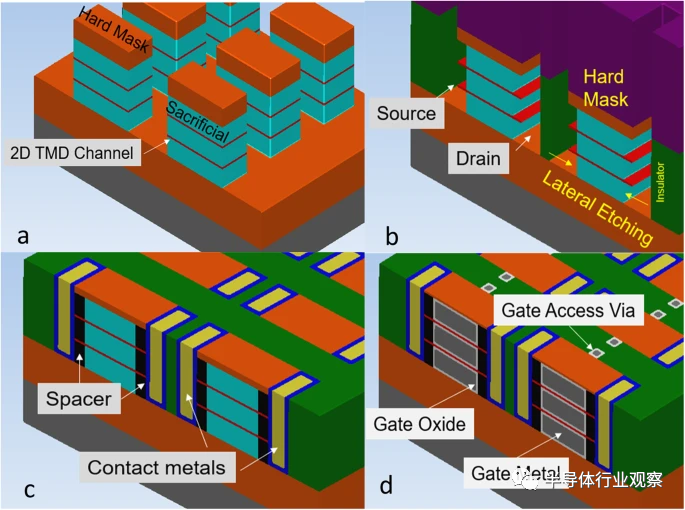

制造二维 TMD NR 晶体管必须包括以下关键工艺步骤:(1) 二维 TMD 的沉积,(2) 叠层 NR 沟道的形成,(3) 间隔区的掺杂,以及 (4) 源极/漏极接触区和栅极氧化物/金属区的沉积。在图3中,我们分享了一个简化的二维TMD叠层NR集成方案,以提请读者注意目前文献中报道较少的挑战。在图 3a 中,我们展示了一个切割后的二维叠层 NR 结构图像,二维片之间有一个牺牲氧化层隔开,这揭示了制造过程中众多挑战中的第一个,即蚀刻对二维沟道性能的影响。在最终产品中,由于 NR 的宽度可以小到 5-10 nm,因此 NR 边缘的缺陷和边缘终止可能会影响器件的性能。在图 3b 中,我们展示了使用定向和各向同性蚀刻形成间隔区的过程。现代硅技术中使用的许多蚀刻溶液并不能转化为二维 TMD 叠层 NR 结构,而且人们对干法、湿法和气相蚀刻化学法与二维 TMD 的相互作用仍然知之甚少。因此,我们需要能在不损害 TMD 单层的情况下去除周围材料的选择性化学方法。

图 3:将二维TMD沉积或转移到牺牲氧化物上的简化二维TMD叠层NR集成方案。

为便于说明,我们将图片限定为两个堆叠的 NR。红色代表 TMD,浅蓝色代表牺牲膜(可以是氧化物或其他材料)。a对堆叠的二维 TMD NR 进行蚀刻。b 侧面蚀刻,打开源极和漏极接触区,形成内部间隔。c通过大马士革工艺(damascene process)形成金属触点(蓝色和黄色层)。d通过原子层沉积 (ALD) 工艺蚀刻通路以填充栅极氧化物(浅灰色)和金属(深灰色),从而形成栅极。请读者注意,由于二维TMD范德华(van der Waals)材料的性质,栅极氧化物沉积具有独特的挑战性。典型的原子层沉积工艺依赖于悬挂键进行材料成核,但无缺陷的二维 TMD不存在悬挂键。

在图3c和d中,我们展示了源极/漏极接触和栅极氧化物/金属沉积的形成过程。要形成源极/漏极接触区,必须考虑两个关键因素:暴露的二维薄膜面积和暴露材料的质量,后者可能会因蚀刻工艺而改变。虽然特定的制造方案可以在接触区暴露出更大面积的二维薄膜,但也可能使二维 TMD 表面质量下降,从而增加接触电阻或导致机械不稳定性。其他没有明确解决方案的挑战是如何掺杂间隔物下的二维薄膜,以及最佳方案是依靠置换掺杂还是远程电荷掺杂。

由于TMD在制造过程的多个阶段仅在2或3个面上得到支撑,因此单层薄膜的机械坚固性非常令人担忧。例如,在图3b中,TMD 层只有两面受到绿色绝缘层的支撑,一面受到蓝色牺牲氧化层的支撑,剩下的一面在内层间隔物沉积之前对空气开放。幸运的是,TMD的特点是单层 MoS26 的杨氏模量(robust Young’s)高达约 270 兆帕,而 Si7为 130-188 兆帕。在制造过程中,内应力和周围薄膜热膨胀的影响可能是一个问题,如果使用湿蚀刻工艺,毛细管塌陷也是一个问题。考虑到这些因素,我们需要更多的非侵入式解决方案来蚀刻 TMD周围的薄膜,同时又不破坏其特性。一种缓解策略是在制造 TMD 纳米带时加入牺牲背层,以提供机械支撑。

接触区和间隔层下的掺杂也将是未来 TMD 器件面临的一项挑战。目前,掺杂 TMD 材料有两种通用方法,一种是置换掺杂,另一种是远程电荷掺杂。过去,通过将掺杂原子高能植入硅晶格来实现硅的置换掺杂。然而,由于 TMD 的单层性质,这种方法无法应用于叠层 TMD 纳米带。替代性掺杂需要重新生长 TMD 薄膜或极其复杂的制造技术。TMD 的另一种独特可能性是在通道附近放置偶极子电荷,以有效掺杂相关区域。然而,这种策略可能会引入来自相同偶极子的潜在库仑散射(coulomb scattering ),因此需要进一步调整。

与硅一样,纳米带堆叠结构的选择也会对多个领域和设计决策产生深远影响8。在图 3 中,我们分享了一种制造堆叠纳米带结构的方法,该方法基于单一类型的 TMD 作为 NMOS 和 PMOS 器件的半导体通道。对于堆叠在PMOS路线上的NMOS,有可能为 NMOS 和 PMOS 晶体管分别使用不同的材料。由于要权衡驱动电流和电池电容,这些结构的最佳设计仍是一个未决问题。

在二维TMD上沉积栅极氧化物

沉积符合严格的可靠性和等效氧化物厚度 (EOT) 要求的栅极氧化物仍然是一个持续的研究课题9,10。例如,栅极氧化物厚度需要扩展到约1nm的电气EOT,同时满足氧化物击穿要求,以及基于体积限制的<3 nm的物理厚度。图3d显示了栅极氧化物/金属沉积的示例。二维TMD是没有悬键的范德华材料(van der Waals materials )。由于原子层沉积 (ALD) 依赖于悬键来启动生长并可控地合成有限的介电厚度,因此在具有最小缺陷的二维 TMD 表面进行栅极氧化物的 ALD 生长是一项重大挑战。我们以前曾报道过物理吸附可以增强栅极沉积10,而破坏较厚的TMD作为替代栅极的策略可能会产生不必要的滞后,在栅极长度低于10 nm时无法达到低SS。在图 4a 中,我们展示了GAA沉积,但要获得理想的最终产品,仍需解决器件集成的难题。此外,器件可能无法通过可靠性测试。栅极堆叠技术的另一个相对尚未探索的方面是使用不同的工作函数金属或偶极层来设置多个NMOS和 PMOS 门限电压。如果要在前端晶体管技术中使用二维材料,这是一项关键要求。

图4:二维TMD纳米带的透射电子显微镜 (TEM) 截面图像。

a.带有GAA氧化物和金属的二维 TMD NR,尺寸栏为 10 纳米。b-d.带有Se和W TEM HAADF信号的四个叠层二维 WSe2 NR。

现实的二维TMD生长要求

尽管过去10年中在二维TMD生长质量方面取得了重大进展,但这一领域的研究仍需继续。50多年来,硅一直是晶体管的首选材料,其原因之一就是存在缺陷密度极低的晶体外延生长工艺。二维TMD生长目前还没有达到单晶水平:已经证实晶粒尺寸大于10微米,但很少能获得晶圆级无缺陷单晶薄膜11。二维TMD沉积通常是一个随机过程,在晶圆上的随机位置开始生长,晶体横向生长,最终合并成多晶材料。由于大多数生长技术都具有随机性,晶界的随机分布会导致不同器件的沟道质量存在差异。如果传输特性存在显著差异,器件性能的变异性就会过大,无法满足现代电路设计的要求2。为了规避这一问题,我们之前已经引入了在确定位置选择性生长 TMD 晶体的方法,但这种方法也面临着自身的集成挑战12。进一步发展二维 TMD 沉积技术,生产出具有大晶粒尺寸和低缺陷密度的凝聚单层薄膜,将有助于缩小高质量硅外延和二维 TMD 生长之间的差距。值得注意的是,这个问题也可能是一个干扰因素,因为晶体管的驱动电流通常由10纳米以下栅极长度的接触电阻所主导。因此,沟道迁移率的变化可能与驱动电流的变化关系不大。

接触电阻

TMD的接触电阻可以说是需要解决的最关键问题,在过去几年中,相关领域已经取得了重大进展。尽管如此,如果要使TMD达到商用半导体产品的水平,还需要继续研究二维TMD 的 NMOS 和 PMOS接触电阻。随着锑(Sb)和铋(Bi)等半金属的引入,NMOS接触电阻在过去几年中取得了快速进展。Bi的熔点较低,仅为 271°C,而Sb则能在 BEOL 温度下进行加工,因此更受青睐1,13。然而,这些半金属能否在10-20 纳米的物理接触尺寸要求下达到严格的接触电阻率目标,目前仍是未知数。PMOS接触电阻仍然是一个难以捉摸的问题。我们发现,如果WSe2的质量足够好,Ru等金属是PMOS WSe2系统的良好候选材料1。二维材料的接触电阻仍然是二维TMD性能的致命弱点,我们强烈鼓励在这一领域开展更深入的研究。

由于前端硅晶体管正在转向GAA NR架构,因此二维TMD也将采用类似的几何结构,以提高竞争力。这就带来了一个潜在的问题,因为大多数已发表的试图解决接触电阻问题的作品都是基于蒸发顶部触点,而最简单的NR晶体管制造却默许使用边缘触点,如图 3c 所示。通过改变图3c中的蚀刻顺序,使内隔板向栅极蚀刻的程度大于图中所示的程度,就有可能用ALD金属制作出部分环绕触点。但是,这可能会影响晶体管密度。另一种方法是在接触区重新生长TMD。在这种情况下,我们鼓励科学界向GAA架构发展,因为未来的器件学习将提供宝贵的反馈,并加速实现潜在的集成。

未来方向

总之,我们强调了二维 TMD 晶体管有机会取代硅晶体管的原因,特别是在10纳米以下的栅极长度。此外,我们还强调了需要进行更多学术和工业研究的领域,以及实现这一转变的基本认识。这些重要领域中的每一个,即 (1) 二维 TMD 的沉积,(2) 堆叠 NR 沟道的形成,(3) 间隔区的掺杂,以及 (4) 源极/漏极区和栅极氧化物/金属区的沉积,都需要可行的可制造解决方案。此外,我们还注意到,虽然未来的硅器件架构是以NR为基础的,但目前的TMD文献主要集中在背栅器件上。我们急需开展更多研究,以了解NR几何形状对二维 TMD晶体管性能的影响。我们必须认识到,这有可能成为类似硅微电子革命的战略拐点。现在是该领域令人兴奋的时刻,我们鼓励开展更多研究,以了解原子尺度的二维TMD NR 架构的物理学和工程学。学术界和产业界都需要加快对这些结构的研究和学习,因为我们正在离开纳米技术世界,进入埃米时代。我们需要专注于制造、控制和理解极其复杂的系统,在这些系统中,每个原子都至关重要。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学