精心设计的互连对于实现异构集成和小芯片的优势至关重要。随着芯片行业逐渐由单片平面芯片模式演进至封装内芯片与小芯片集成的趋势,设计和制造互连变得越来越复杂,对设备可靠性也越来越重要。曾经简单的铺设一条铜导线这样简单的事情已经演变成数以万计的微凸块、混合键合、硅通孔 (TSV) 甚至光纤接头。主要目标仍然是使用尽可能低的功率,以最小的 RC 延迟尽快将信号从 A 点发送到 B 点,同时确保这些信号完好无损并到达目的地。但让所有这些工作发挥作用是一个越来越大的挑战。随着数据速率的提高,我们突破了物理通道上可以推送的数据的极限,将需要并行处理或嵌套并行处理来提高速度。这意味着比以往任何时候都需要更多的互连。这对于小芯片来说是显而易见的,其中数据需要流入和流出小芯片以将其连接到封装中的其他组件。这种方法可能更复杂,但在功率方面有显著的回报。相关研究人员表示:“常规芯片的输出引脚上有大功率驱动器,这些驱动器的强度足以通过 PCB 上相对较大且较长的信号迹线驱动电信号。但是小芯片不需要那些真正大的驱动器,因为 2.5D 互连要小得多,因此您可以在每个芯片上使用更小的 I/O 驱动器来节省空间和功耗。这种转变的主要原因是将更多功能封装到固定区域的物理原理。虽然数字逻辑将扩展到单埃范围,但缩小线径会增加电阻和电容,同时增加一系列新的物理效应。设备可能运行得更热,信号可能运行得更慢,并且信号完整性变得更难以维护。克服这些问题需要具有更高电子迁移率和更广泛的关键数据路径的新材料。它还需要深入了解设备在不同工作负载下的运行方式,这可能会影响沿 x、y 和 z 轴互连的整体布局。将芯片上原来的内容分解为更广泛的多个小芯片。芯片上的通信方式需要扩展到小芯片之间的通信方式,但这与在小芯片之间使用的基板无关。芯片上的模块的复杂性已经增加。随着 90 年代末芯片变得越来越大,业界开始关注如何连接它们,从而出现了虚拟套接字集成方案和针对每种情况量身定制的各种总线。由于块的数量变得难以管理,因此出现了测试总线、高性能总线、外围总线等。随着时间的推移,总线系统变得过于耗能,这导致了协议的开发以减少开销。人们开始通过创建高级微控制器总线架构(AMBA) 来解决这一问题,这是一种用于 SoC 中模块连接和管理的开放标准。在过去的 30 年里,AMBA 进行了修订和扩展,制定了多个二级协议。最近,新的CHI C2C 规范公布,将 AMBA 扩展到 Chiplet。丰富的互连PHY和协议在某种程度上带有讽刺意味。单片芯片早期的巨大优势之一在于其内部无需互连,因为所有的组件都是在同一个工艺步骤中制作的。有观点指出,随着系统中互连数量的增加,系统的可靠性会逐渐降低。然而,现实中我们看到的是,现在的系统拥有更多的互连。即便是普通的2.5D设计,也可能轻易拥有高达500,000个互连点。

另一方面,可靠性复杂化可能是技术进步的必然产物。随着组装技术的进步,如从焊球到铜柱,再到混合键合,我们可能会面临一些新的可靠性问题。特别是在小芯片接口方面,由于某些区域的互连数量极高,这可能带来新的挑战。尽管如此,精心设计的互连对于实现异构集成和小芯片技术的优势至关重要。随着信号数量的增加和数据量的不断增长,这些信号和数据需要在日益复杂的布局中传输。由于大量的连接可能导致延迟增加,互连可能成为系统性能的瓶颈。有专家指出,系统的整体速度往往受限于设计中最慢的互连部分。因此,优化互连设计对于提高系统性能至关重要。

在多层集成电路设计中,薄的、短的局部互连负责实现片上的连接功能,而厚的、长的全局互连则负责在不同块之间传输信号。硅通孔(TSV)技术使得信号和功率能够轻松地从一层传输到下一层。

相较于传统的PCB互连,2.5D(以及未来的3D-IC)小芯片互连技术展现出其独特的优势。它拥有更薄、密度更高的互连,并且通常距离也更短。此外,诸如TSV、微凸块和混合键合等新技术使得互连图变得更为复杂,特别是在3D集成中。

从积极的角度看,这种技术意味着2.5D小芯片之间的通信速度更快、带宽更高、功耗更低。然而,它也存在不足之处,即相较于PCB技术,成本更高。众多高速信号的设计需要进行全面的电磁耦合分析,这比仅停留在芯片层面上所使用的简单RC建模要复杂得多。

然而,随着IR压降和RC延迟等问题开始影响性能,业界正在考虑通过芯片背面供电的方式来减少设备上金属层的布线拥塞。这不仅能够保持整个设备的信号完整性,还能确保晶体管获得足够的功率。但这一方案也带来了新的复杂性,大批量制造中尚未完全解决这一挑战。

随着标准的不断变化和更详细的变体的出现,互连解决方案的选择变得更加复杂,它提供了定义的节点。如果查看 SoC 内的互连,会立即想到 AMBA 总线之类的东西。随着流媒体接口、CHI 等扩展的发展,以及在芯片上扩展到更多网络的扩展。可扩展性主要聚焦于异构、块到块拓扑的扩展,以及将SoC分割为多个芯片的网状结构。这一过程因涉及各种协议而变得相当复杂,而不同版本之间的兼容性问题更是加剧了这种复杂性。许多合作方都倾向于选择特定的接口标准,但其中的细节却至关重要:他们采用的是哪个版本?举例来说,最新的Arm内核采用了CHI-e接口,而较老的版本则可能采用CHI-b接口。这意味着在处理版本控制时,我们必须注意不同版本间可能存在的功能差异。因此,充分的沟通与确保兼容性成为了关键所在。

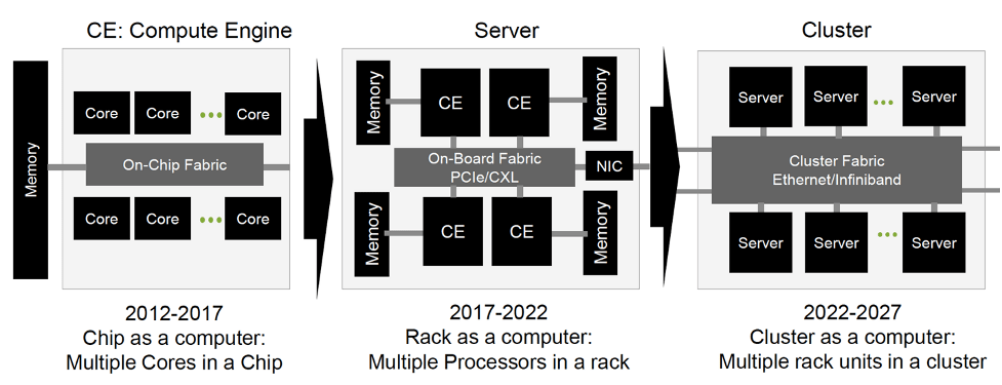

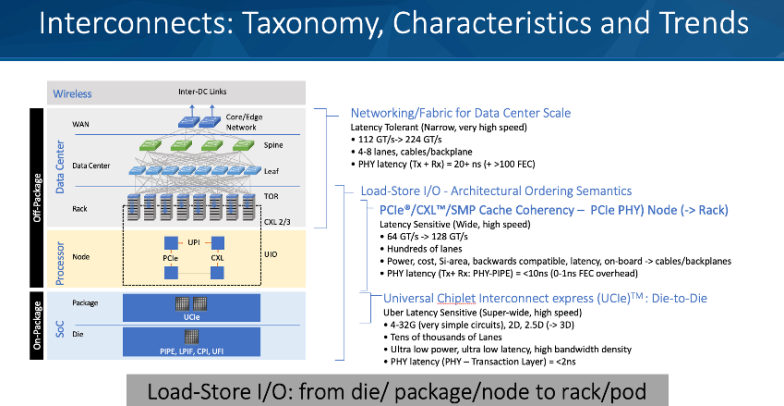

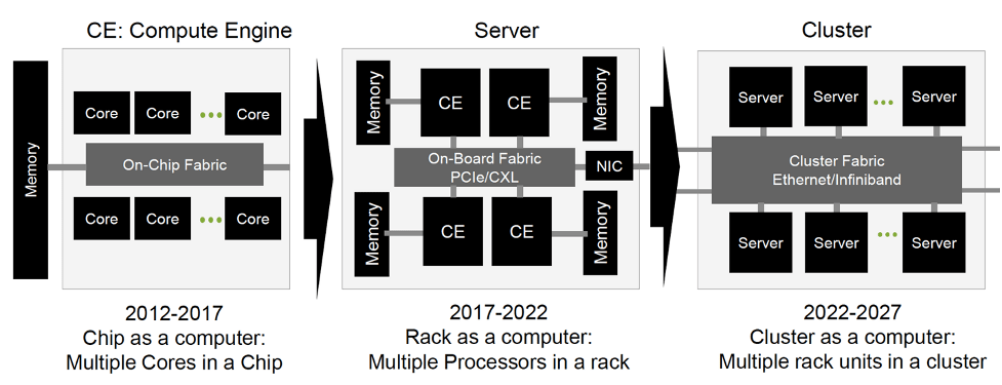

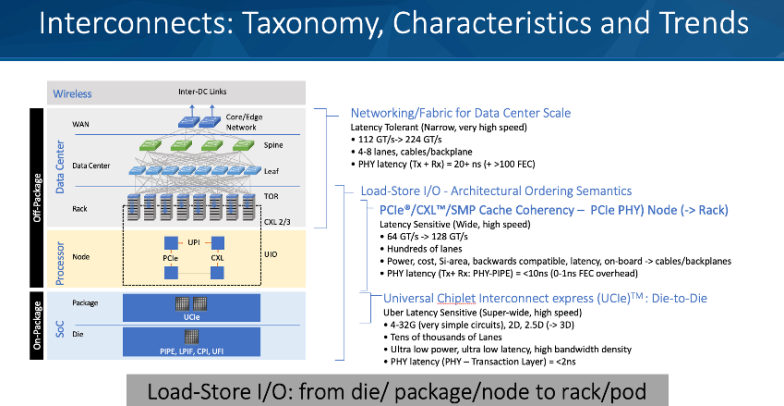

但是协议的激增不太可能、也不应该很快得到遏制。有些人错误地认为应该有一个互连来完成这一切。这是不正确的。相信业界已经聚集在正确的互连集周围——用于封装内的 UCIe、用于封装外的 PCIe 和 CXL、以及机架/pod 级以及用于网络的以太网。

因此,所有这些互连都可以相互通信非常重要,并且互操作性仍然是设计人员的必要目标。为了应对多重互连的这些挑战,业界确实需要一个可纵向扩展和横向扩展的互操作标准。整个生态系统正在努力整合并匹配这种性能。目前部分企业提供了一个可以横向扩展的后端网络,而小部分企业拥有可以提供缓存一致性的开放结构和CXL技术。对于芯片到芯片的分割,UCIe 是最佳选择。这些可互操作的开放标准为解决行业面临的互操作性问题提供了创新。

尽管不同的设计有着各异的互连方式,小芯片互连正明显呈现出标准化的趋势。即便是那些掌握连接两端的用户,也倾向于采用标准,因为他们希望从大型标准组织所付出的集体努力中获益。事实上,我们永远无法拥有足够的工程师来设计所有可能的互连方式,因此,依赖标准能使用户从该领域其他人的集体智慧中学习和进步。

与此同时,先进封装供应链的紧张状况也促使更多的用户考虑采用有机封装。这种封装方式,通常被称为标准封装,不仅有助于缩短周转时间,而且其支持的带宽密度足以满足许多原本认为需要先进封装技术的客户的需求。

然而,随着行业逐步转向小芯片技术,仍然存在一个亟待解决的关键问题。小芯片互连面临的一个重大挑战在于,现在无法像过去那样通过针或探针卡探测来测试接口。如果启动不成功或在运行过程中出现错误,这种测试是必不可少的。因此,我们迫切需要新的解决方案,例如片上监控和测试技术,来应对这一挑战。

随着新的 2.5/3D 封装设计的复杂性日益增加,对新解决方案的需求是一个重要方面,产品开发现已跨学科化,引入了不同的专业领域和不同的分析工具。高速数字、射频、光子学、电力电子、ASIC 设计、热、机械等都必须紧密结合在一起,这是复杂性的一个维度,这些学科通常是相互依赖的,使设计过程进一步复杂化。需求、流程和数据必须在设计、测试和制造的整个工程生命周期中进行管理,这给产品开发工作增加了更多的复杂性。最后,小芯片必须在更高级别的分层系统中运行,因此必须考虑自上而下的设计和自下而上的验证元素。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学