数字IC的高级封装

作者:admin 来源:本站 发布时间:2023-08-17 访问量:3280

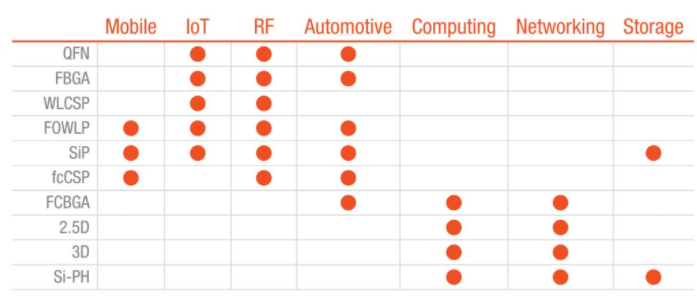

数字 IC 的封装选项(以及相关的流行词和首字母缩略词)继续成倍增加。微处理器、现场可编程门阵列 (FPGA) 和专用定制 IC (ASIC) 等高级数字 IC 以多种封装形式提供,例如:QFN——四方扁平无引线; FBGA——细间距球栅阵列; WLCSP——晶圆级封装; FOWLP——扇出晶圆级封装; fcCSP——倒装芯片级封装;和 FCBGA——倒装芯片球栅阵列封装。

先进半导体器件的封装类型和市场用途 (表:格罗方德)

将多个芯片封装在一起的选项包括系统级封装、多芯片模块、芯片级、小芯片、异构、2.5D 和 3D 堆叠等。正在开发的多芯片量子处理器可以解决容错量子计算机的关键扩展挑战。共同封装光学器件 (CPO) 或封装光学器件 (IPO) 正在出现,它们将光学器件和开关硅集成在同一封装中,从而在曾经不相交和独立的技术之间产生协同作用,并节省大量功率。

小芯片、MCM 和 SiP

基于小芯片(Chiplet)的设计、多芯片模块 (MCM) 和系统级封装 (SiP) 是或可以是异构集成的形式,在定义这三种封装风格时存在非常大的灰色区域。一家公司的基于小芯片的设计可能被另一家供应商称为 MCM,而 MCM 和 SiP 通常被归为同一类别。下面回顾了一些细微差别。

小芯片是经过测试的 IP 功能的物理实现,具有在硅晶片上制造的标准通信接口,可通过提高制造产量和跨应用程序的可重用性来降低成本。给定解决方案中的小芯片可以具有不同的工艺节点。小芯片提供标准功能,使设计人员能够专注于设计中的独特 IP。结果被称为“伪 SoC”,其设计速度比完全集成的 SoC 解决方案更快、成本更低。基于小芯片的解决方案通常不包括无源设备或其他“非硅”设备。小芯片解决方案的一个例子可以是当今的一些微处理器,其中处理器内核和 I/O 驻留在通用封装中的不同硅芯片上。

MCM 最初仅集成多个芯片,不包括无源器件或其他组件。 MCM 中的芯片是“完整”的 IC,例如处理器、GPU 和 RF 部分,而不是更简单的单功能小芯片。随着概念的发展,MCM 的尺寸越来越大并集成了额外的组件,于是 SiP 诞生了。 MCM 和 SiP 之间的主要区别在于 MCM 不必是一个完整的系统。根据定义,SiP 是单个封装中的系统。

MCM 是封装中紧密耦合的子系统或模块。 SiP将多个 IC 以及支持的无源器件集成到单个封装中。与 MCM 一样,SiP 可以使用来自最佳单个工艺或工艺节点的硅来优化性能并实现所需的集成。SiP 被设计为一个完整的系统并用作单个组件。

2.5D 和 3D 封装

使用硅通孔 (TSV) 互连多个管芯通常被认为是 MCM 或 SiP 与 2.5D 封装器件之间的区别。 TSV 为 MCM 和 SiP 中的有机基板提供了高密度替代品。使用 TSV 可以获得 3D 封装的一些好处,而没有与全 3D 方法相关的挑战和成本。简而言之,与传统的 MCM 或 SiP 解决方案相比,将多个管芯放置在具有非常细间距 TSV 的中介层上会产生互连和更好的重量、尺寸和功率特性。

全3D IC则是更进一步,使用 TSV 在垂直维度上堆叠。它可以产生更小和更高性能的解决方案。 3D 封装是另一种形式的垂直集成,指的是使用引线键合和倒装芯片等互连方法进行 3D 集成。 3D 封装可分为 3D 系统级封装 (3D SiP)、3D 晶圆级封装 (3D WLP) 和 3D 层叠封装 (3D PoP)。与 2.5D 封装相比,各种形式的 3D 封装都有一些缺点,包括:通过将芯片并排放置而不是垂直堆叠可以提高散热性能。3D 结构本质上更复杂,修改或升级 2.5D 装配通常更简单、更快。升级 2.5D 器件就像使用新的中介层或用改进版本替换一个或多个芯片一样简单。

2D 封装在封装基板上的单个平面上安装 2 个或更多裸片,2.5D 在裸片和封装基板之间添加一个中介层,3D 堆叠则是在垂直维度进行集成。

晶圆级和芯片级

使用晶圆级封装 (WLP),晶圆制造工艺扩展到包括晶圆切割之前的器件互连。大多数其他封装首先进行晶圆切割,然后将单个管芯放入塑料封装中并连接焊料凸点。 WLP 在切割晶圆之前将封装的底部和顶部输出层以及焊料凸块连接到 IC。由于封装与裸片的尺寸基本相同,因此 WLP 是芯片级封装 (CSP) 技术的一种形式。

WLP 用于需要尽可能最小的解决方案的应用,例如智能手机。然而,WLP 的局限性在于,由于封装尺寸非常小,可以支持的触点数量有限。在高度复杂和紧凑的系统中,扇出晶圆级封装 (FO-WLP) 增强了标准 WLP 以克服有限的 I/O 功能。

与传统封装相比,FO-WLP 可实现更小的封装尺寸以及改进的散热和电气性能。尽管如此,FO-WLP 还是比 WLP 大,而且 FO-WLP 支持更多数量的触点,但不会增加芯片尺寸。在 FO-WLP 中,首先切割晶圆,然后将芯片精确地重新定位在载体晶圆上,每个芯片周围都有一个扇出区域。模具成型,然后添加焊球。

光学封装

高速数字网络(例如超大规模数据中心)中的序列化-反序列化 (SerDes) 功能通常涉及基于硅的通信链路和基于光的链路之间的接口。随着光学引擎和开关硅之间的距离减小,通道插入损耗也随之下降,从而节省了大量功率。最接近的间距是通过共同封装光学器件 (CPO) 实现的,其中接口的两侧都在一个封装中。共同封装的光学器件具有最短的互连距离和最大的节能效果。

多芯片量子处理器

扩展量子计算机具有挑战性。随着量子处理器尺寸的增加,制造良率下降。实现纠错量子计算需要大量的量子位(qubit)。正在努力将多个较小的芯片连接到一个大规模的量子处理器中。这种多芯片方法有望简化大型量子处理器的创建,并支持该技术的可预测和加速扩展。

缩放是开发容错量子计算机的关键。预计今年晚些时候将测试一个 80 量子位的系统。将多芯片模块技术应用于量子处理器可以产生足够大的系统来运行实际应用,包括所需的纠错。

数字 IC、光互连和量子处理器的封装选择越来越多。先进的封装技术支持异构集成以及使用来自最佳单个工艺或工艺节点的 IC 来优化性能并实现所需的集成。持续的封装开发对于实现从手机到超大规模数据中心的先进系统解决方案非常重要。

来源: EEWORLD

上一篇:电源转换类芯片

下一篇:关于SiP与先进封装的异同点

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学