堆叠纳米片和叉片 FET

作者:admin 来源:本站 发布时间:2022-01-05 访问量:2936

在全栅 FET仍在制定之后,接下来会发生什么,但它可能会涉及某些版本的堆叠纳米片。

先进晶体管的设计是一种权衡。一方面,控制细沟道所需的栅极电容更少。另一方面,细通道不能承载那么多的驱动电流。

堆叠纳米片设计试图通过使用多个薄通道来调和这两个目标,每个通道都有自己的栅电极。尽管这些器件类似于finFET,但堆叠纳米片工艺流程引入了几个新模块,并且在 6 月的 VLSI 技术研讨会上的演讲考虑了这些新模块如何对整体性能做出贡献。

纳米片晶体管通常以 Si/SiGe 异质结构开始,层对的数量与成品器件的通道数相同。这种结构可以作为硅或硅锗通道的起点。

Imec 的 CMOS 逻辑器件技术项目主管 Naoto Horiguchi 解释说,虽然最终可能需要 SiGe 更高的迁移率,但大多数堆叠纳米片晶体管演示目前使用 SiGe 作为牺牲层。通常,硅纳米片是未掺杂的。栅极金属的功函数定义了阈值电压。

硅层和硅锗层之间的界面决定了最终的通道质量。Applied Materials 副总裁 Kevin Moraes 强调需要突然的、原子级平坦的过渡。为了最大限度地减少成品器件中的寄生效应和高频损耗,层与层之间的间距应在可制造性范围内尽可能小。

图 1:堆叠纳米片工艺流程。资料来源:Imec

接下来的几个步骤与典型的 finFET 工艺一样进行,包括鳍图案化、隔离和伪栅极的形成。然后,在沉积外延源极和漏极层之前,内部隔离物限定了栅极和源极/漏极之间的间隙。内部隔离物的形成包括选择性的蚀刻 SiGe 层中的凹槽,然后用介电材料填充它。

与平面晶体管中的隔离物一样,内部隔离物的尺寸至关重要,因为该隔离物对齐栅极并有助于控制泄漏和寄生电容。它还起着重要的结构作用——源极/漏极外延之后是沟道释放蚀刻,去除 SiGe 并使沟道层仅在边缘得到支撑。

韩国忠北国立大学的 Khwang-Sun Lee 和 Jun-Young Park表明,内间隔件的轮廓和机械性能可以使整个结构或多或少地变形。过度应变会引起可靠性问题,并影响载流子迁移率和其他器件参数。

在沟道释放蚀刻之后,首先是栅极电介质,然后是栅极金属填充间隙。纳米片之间的空间需要足够大,以允许去除蚀刻残留物、沉积和去除牺牲栅极,最后沉积栅极电介质和栅电极。

在替换栅极工艺中,一半的器件被掩蔽,而另一半的牺牲栅极金属被去除。然而,在堆叠的纳米片结构中,此步骤的掩模不仅必须保护表面,还必须保护堆叠的暴露侧。N 型和 P 型器件之间的最小间距受到光刻工艺定义该掩模的能力以及在金属蚀刻过程中避免底切掩模的需要的限制。此外,蚀刻工艺必须有足够的选择性以防止掩模边缘的腐蚀,这会影响栅极尺寸。

降低标准单元高度的需求有助于推动纳米片设计的引入。由金属间距定义的单元高度确定了互补 N 型和 P 型器件之间的最大间距。反过来,两者之间的最小间隙定义了通道宽度,从而定义了可用的驱动电流。在此步骤中制造的沟槽需要越宽,留给载流沟道材料的空间就越小。

这种最小化 NP 间距的需求激发了 Imec 的“叉板”设备设计。在一次采访中,Horiguchi 解释说,故意调整鳍片蚀刻工艺允许 Imec 在器件鳍片之间产生低于 20 纳米的间隙。他们用氮化硅壁填充了这个间隙,作为 N 型和 P 型器件之间的绝缘体和蚀刻停止层。Forksheet FET 的性能可与同一晶片上的全栅纳米片参考器件相媲美,但 N 型和 P 型器件之间只有 17 纳米的间距。

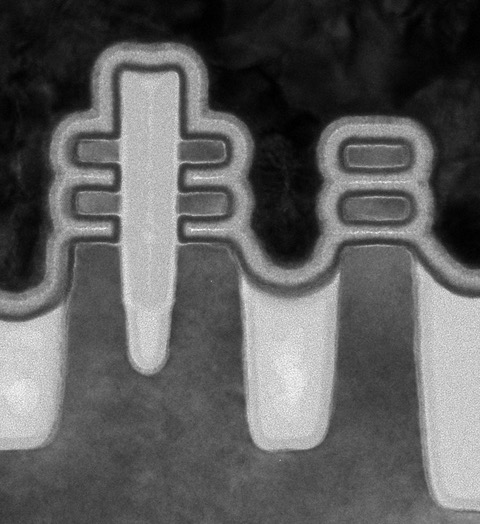

图 2:N 和 P 型叉片 FET 对(左)和堆叠纳米片 FET(右)。来源:imec

Forksheet FET 和其他堆叠纳米片设计表明,尽管 2D 半导体具有潜在优势,但硅尚未完成。

上一篇:未来的芯片封装趋势

下一篇:芯片制造中越来越多的数据问题

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学