基于小芯片的晶圆级 AI 引擎中的 14,336 个 ARM 内核

作者:admin 来源:本站 发布时间:2022-07-18 访问量:2653

美国研究人员在拥有 14,336 个 ARM Cortex M3 内核的全球最大晶圆级机器学习引擎中使用了 2048 个小芯片。

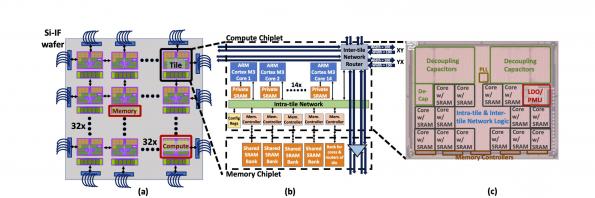

加州大学洛杉矶分校和美国伊利诺伊大学的研究人员在晶圆级互连基板上集成了预先测试过的已知良好的未封装裸芯片或小芯片。该系统包括 1024 个小块的阵列,其中每个小块由两个小芯片组成,总共 2048 个小芯片和大约 15,000 mm 2的总面积。

“据我们所知,这是有史以来最大的基于小芯片组装的系统,”该团队在最近的一篇论文中说。“就活动区域而言,我们的原型系统比 Nvidia/AMD 的单个基于小芯片的系统大约 10 倍,比来自 Nvidia 的 64 个小芯片 Simba 研究系统大约 100 倍。”

相比之下,Cerebras 的第二代 AI 系统在单个晶圆上拥有 850,000 个优化的张量核心,面积为 46,225 平方米。

加州大学洛杉矶分校开发的基于小芯片的晶圆级系统使用硅互连结构 (Si-IF) 将许多小芯片紧密集成在高密度互连晶圆上的基于细间距铜柱(10μm 间距)的 I/O 上,这些 I/O 至少为比基于中介层的系统中使用的传统 µ-bumps 密度高 16 倍,以及~100µm 的小芯片间距。

这些小芯片可以采用异构技术制造,并且可以潜在地提供更好的性价比权衡,100s Tbit/s 的 TB 内存以及高性能计算和 AI 应用程序的 PFLOP 计算吞吐量。

“这个原型系统的规模迫使我们重新思考设计流程的几个方面。因为这是构建这样一个系统的第一次尝试,所以在制造和组装过程中有几个未知数,”该团队在论文中说。“因此,容错和弹性是我们做出设计决策背后的主要驱动因素之一。我们还确保设计决策不会太复杂,这样他们就可以由一个小团队可靠地实施,”他们说。

每个 tile 由两个小芯片组成:一个计算小芯片和一个内存小芯片。每个 40nm 计算小芯片包含 14 个独立可编程的 ARM Cortex-M3 处理器内核和 64kbits 的本地 SRAM,而内存小芯片提供 512KB 的全局共享内存。该系统被构建为一个统一的内存系统,其中任何区块上的任何内核都可以使用互连直接访问整个晶圆级系统的全局共享内存。

小芯片采用 TSMC 40nm-LP 工艺设计和制造,并终止于构建细间距 I/O 焊盘的顶部铜金属层。晶圆级基板是一个无源基板,包含小芯片和铜柱之间的互连布线,以连接到小芯片 I/O。小芯片倒装芯片键合到晶圆级基板上,并通过边缘连接提供功率。

由于晶片基板的尺寸远大于掩模版的最大尺寸,因此必须将 Si-IF 基板设计为可步进重复。整个晶片被分成较小的相同光罩,并通过缝合这些光罩制造,每个光罩由 72 个瓦片 (12x6) 组成。每个标线内的小芯片间链接的宽度为 2 µm,间距为 3 µm,但在每个标线的边缘,链接逃逸变得更粗(宽度增加到 3 µm,间距减小到 2 µm),同时保持间距不变,以减少标线拼接误差的影响。

来自网格边缘每个瓦片的多个 I/O 需要扇出到晶圆边缘并连接到外部连接器,因此扇出布线和边缘 I/O 焊盘被设计成每个标线。来自边缘光罩的 Si-IF 基板上的小芯片插槽将保持未填充状态,并且外部连接器将连接到这些光罩中的焊盘。

为确保这些 I/O 焊盘不会导致小芯片粘合的问题,该团队使用自定义块蚀刻工艺去除不需要的焊盘。如果代工厂支持每个晶片有多个光罩,也可以使用单独的掩模印刷晶片的边缘。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学