晶圆大多是非常脆的硅基材料,直接拿取是非常容易脆断的,所以必须封装起来,并且把线路与外部设备连接,才能出厂。本文详述芯片的封装工艺和相关的设备。封装听起来似乎就是包装,好像比较简单。封装与蚀刻和沉积相比,在一定程度上是要简单一点,但封装同样是一个高科技的行业。传统封装的目的是将切割好的芯片进行固定、引线和封闭保护。但随着半导体技术的快速发展,芯片厚度减小、尺寸增大,及其对封装集成敏感度的提高,基板线宽距和厚度的减小,互联高度和中心距的减小,引脚中心距的减小,封装体结构的复杂度和集成度提高,以及最终封装体的小型化发展、功能的提升和系统化程度的提高。越来越多超越传统封装理念的先进封装技术被提出。先进封装(Advanced Packaging)是本文讨论的重点。

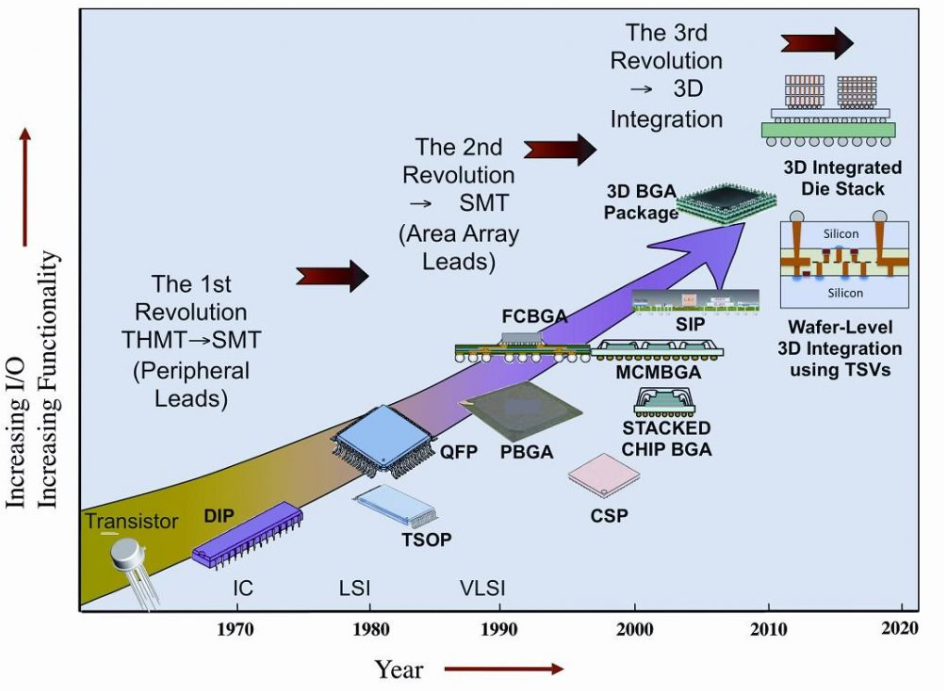

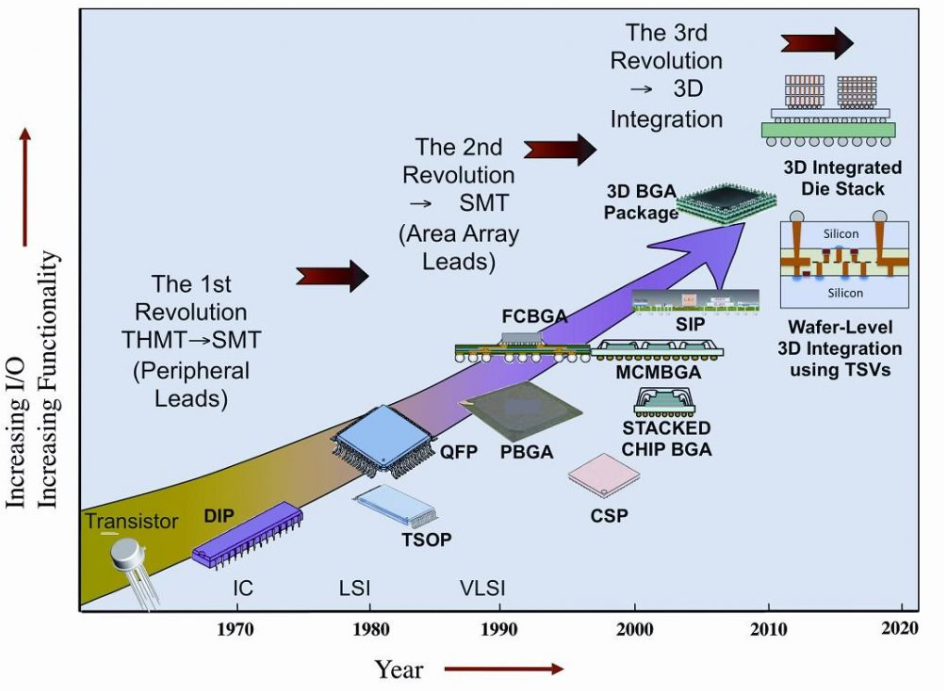

我们先了解一下传统封装,这有利于更好地理解先进封装。传统封装技术发展又可细分为三阶段。

阶段一(1980 以前):通孔插装(Through Hole,TH)时代

其特点是插孔安装到 PCB 上,引脚数小于 64,节距固定,最大安装密度 10 引脚/cm2,以金属圆形封装(TO)和双列直插封装(DIP)为代表;

阶段二(1980-1990):表面贴装(Surface Mount,SMT)时代

其特点是引线代替针脚,引线为翼形或丁形,两边或四边引出,节距 1.27-0.44mm,适合 3-300 条引线,安装密度 10-50 引脚/cm2,以小外形封装(SOP)和四边引脚扁平封装(QFP)为代表;

阶段三(1990-2000):面积阵列封装时代

在单一芯片工艺上,以焊球阵列封装(BGA)和芯片尺寸封装(CSP)为代表,采用“焊球”代替“引脚”,且芯片与系统之间连接距离大大缩短。在模式演变上,以多芯片组件(MCM)为代表,实现将多芯片在高密度多层互联基板上,用表面贴装技术组装成多样电子组件、子系统。

自20世纪90年代中期开始,基于系统产品不断多功能化的需求,同时也由于芯片尺寸封装(CSP)封装、积层式多层基板技术的引进,集成电路封测产业迈入三维叠层封装(3D)时代。这个发展阶段,先进封装应运而生。

先进封装具体特征表现为:

(4)倒装连接、TSV硅通孔连接成为主要键合方式。

先进封装提高加工效率,提高设计效率,减少设计成本。先进封装工艺技术主要包括倒装类(FlipChip,Bumping),晶圆级封装(WLCSP,FOWLP,PLP),2.5D封装(Interposer)和3D封装(TSV)等。以晶圆级封装为例,产品生产以圆片形式批量生产,可以利用现有的晶圆制备设备,封装设计可以与芯片设计一次进行。这将缩短设计和生产周期,降低成本。先进封装以更高效率、更低成本、更好性能为驱动。先进封装技术上通过以点带线的方式实现电气互联,实现更高密度的集成,大大减小了对面积的浪费。SiP技术及PoP技术奠定了先进封装时代的开局,如Flip-Chip(倒装芯片), WaferLevelPackaging(WLP,晶圆级封装),2.5D封装以及3D封装技术,ThroughSiliconVia(硅通孔,TSV)等技术的出现进一步缩小芯片间的连接距离,提高元器件的反应速度,未来将继续推进着先进封装的进步。

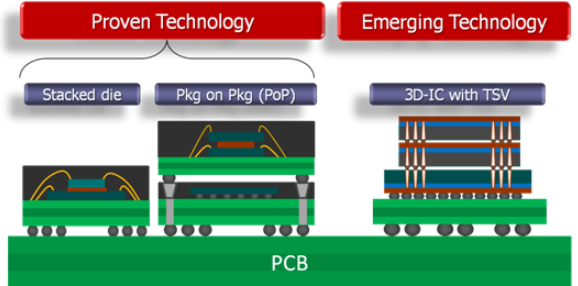

所有这些先进封装技术,被集中起来发展成为了3D封装。3D封装会综合使用倒装、晶圆级封装以及 POP/Sip/TSV 等立体式封装技术,其发展共划分为三个阶段:

第一阶段:采用引线和倒装芯片键合技术堆叠芯片;

第二阶段:采用封装体堆叠(POP);

3D封装可以通过两种方式实现:封装内的裸片堆叠和封装堆叠。封装堆叠又可分为封装内的封装堆叠和封装间的封装堆叠。

最后,我们列举一下这些主要的先进封装技术:

★ 晶圆级封装(WLP-Wafer level package)★ (POP/Sip/TSV)等3D立体式封装技术

它是特指半导体集成电路元件(IC芯片)的封装,芯片由半导体厂商生产,分为两类,一类是系列标准芯片,另一类是针对系统用户特殊要求的专用芯片,即未加封装的裸芯片(电极的制作、引线的连接等均在硅片之上完成)。分为单芯片封装和多芯片封装两大类。前者是对单个裸芯片进行封装,后者是将多个裸芯片装载在多层基板(陶瓷或有机材料)上进行气密闭封装构成MCM。它是指构成板或卡的装配工序。将多个完成层次2的单芯片封装在PCB板等多层基板上,基板周边设有插接端子,用于与母板及其它板或卡的电气连接。将多个完成层次3的板或卡,通过其上的插接端子搭载在称为母板的大型PCB板上,构成单元组件。它是将多个单元构成(框)架,单元与单元之间用布线或电缆相连接。

它是将多个架并排,架与架之间由布线或电缆相连接,由此构成大型电子设备或电子系统。

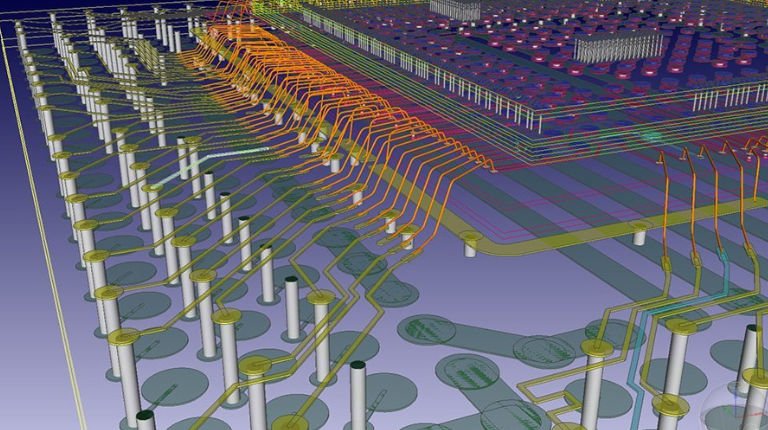

先进封装的主要设备

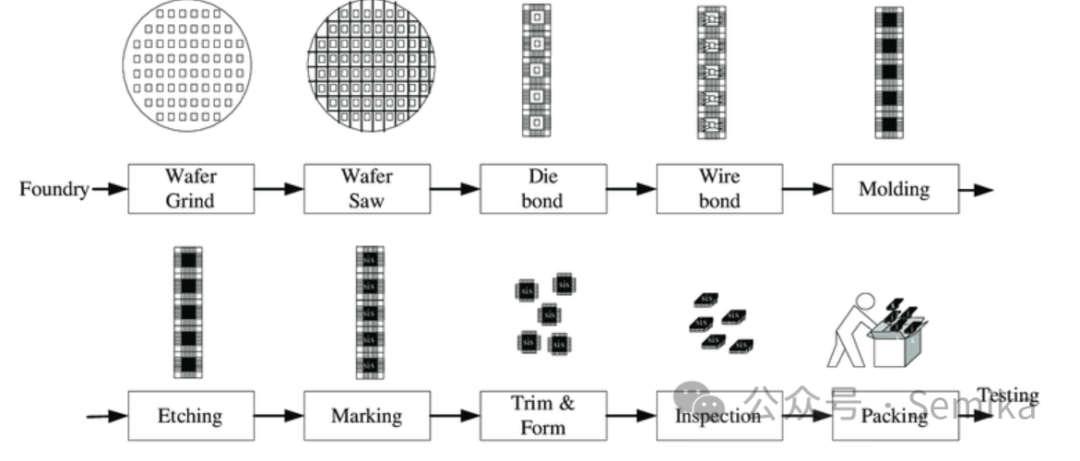

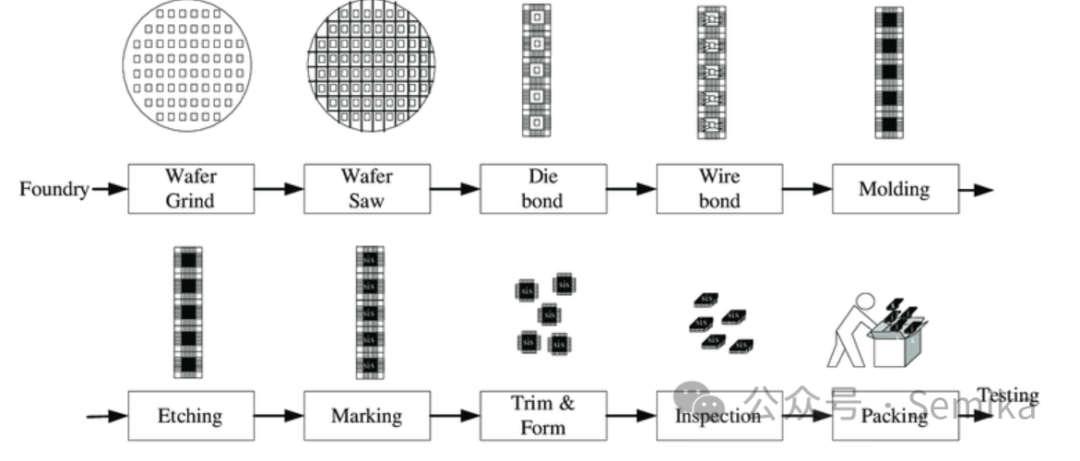

了解了封装的工艺,再来看看有哪些实际的操作要做,所需的设备就明确了。这里按工艺步骤列举一些:

- 裸片堆叠。需要晶圆级叠片机。这是一个对可靠性要求极高的设备,因为线路完成后的晶圆很昂贵,而且非常易碎,更重要的对叠片的精度要求更高。目前还没有国产量产的设备。

- 晶圆切割。将Wafer切割成单个芯片。常见有切割机(Saw锯切)、划片机、激光切割机等。

- 芯片堆叠。这个设备的难度在于精度和速度。目前国内有多家厂商在研发这类设备,主要还是速度(产能)方面的差距。

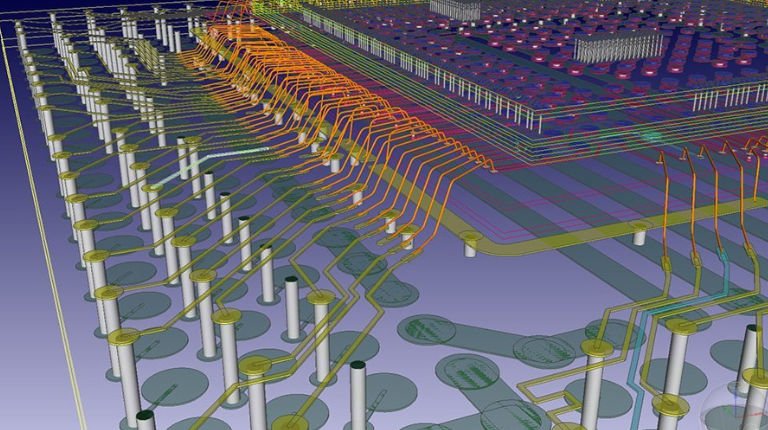

- 封装级光刻蚀刻。这是光刻技术练兵的场所,这里的光刻精度是微米级的,精度高一点的也达到了0.1微米。

- 贴片(把芯片放在基板上)。这一过程需要用到点胶机,贴片机/固晶机/键合机等主要设备,还要用到印刷机,植球机,回熔焊,固化设备,压合设备,清洗设备等。

- 引线键合。主要有Wire bound和Die Bound两类设备。

- 置散热片、散热胶、外壳。这一过程也要用到点胶,灌胶,植片机/固晶机/贴片机,压压合设备,清洗设备等主要设备。

检验。包括检验、测试和分选。

封装所涉及设备比较多,在此先列举这么多。以下流程图可供参考

1、清洗机

这些设备中,清洗机听起来相对简单,但清洗机也绝对不是那么的简单。清洗的优劣,决定着产品的良率,性能及可靠性。有时更决定着工艺过程的成败。

接触芯片的零件的清洗,对尘埃、油污的要求,都是绝对严苛的,有的还要对零件表面的挥发气体进行测量,对表面对不同物质的亲合性进行测量。而要达到这些要求,对清洗工艺的要求也往往非常复杂。一条清洗线也动辄十几道 ,几十道工艺过程,对零件进行物理的、化学的、生物级别的清洗与干燥。

2、涂胶设备

封装阶段的胶水,作用一是把IC的不同部分粘结起来,作用二是把IC各个部分之间的间隙填充起来,作用三是把IC包裹保护起来。这也就基本形成了三个类别,一是点胶,二是填充,三是塑封(Moding)。这些工艺过程,听起来比较简单,很容易理解。事实也确实如此。只是对胶量的控制,均匀性有很高的要求。胶水的压力,出胶口的形状,温度,运动的平稳性,设备的振动,空气流动等,每一个环节都要精确控制。涂胶的工艺的特性主要的还是决定于胶水的特性。在这里我们只谈设备,不谈耗材。

芯片点胶

芯部底填

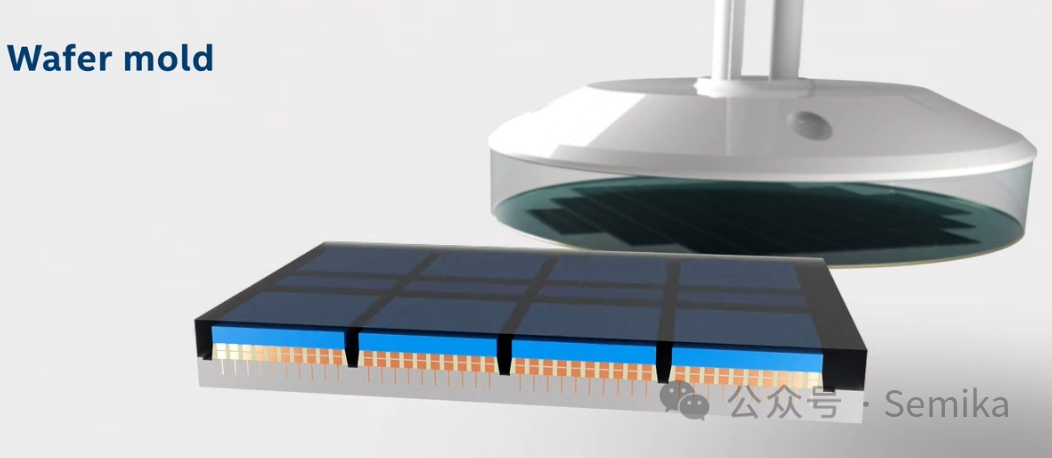

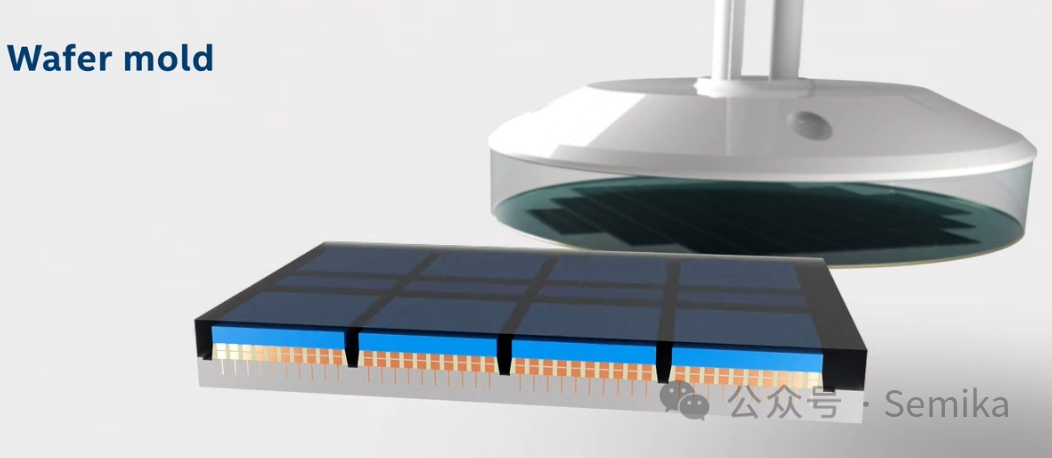

芯片塑封

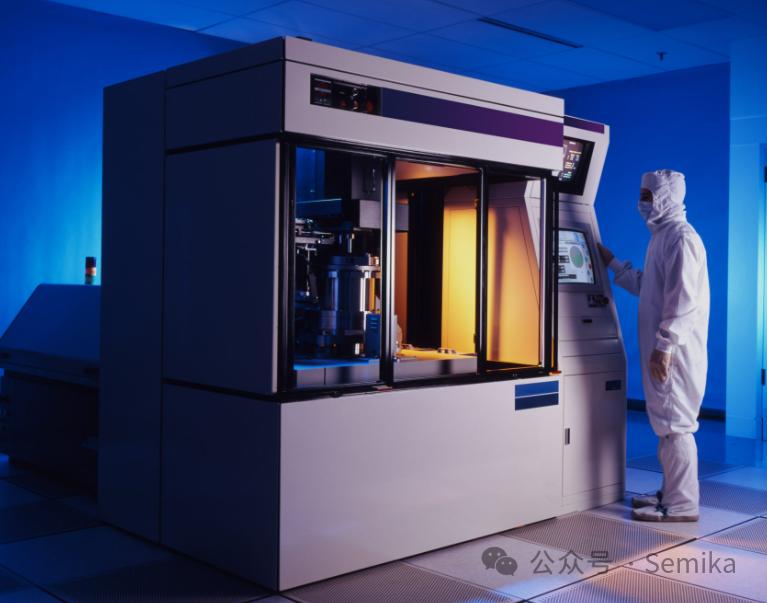

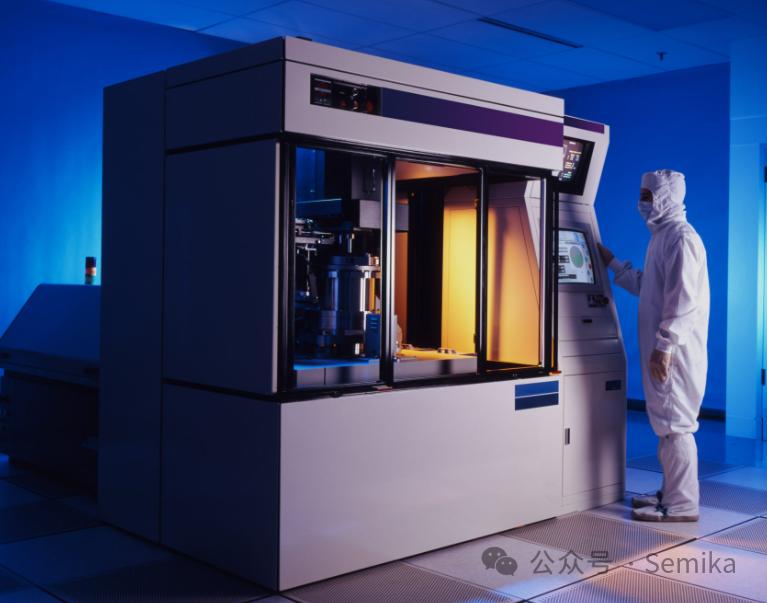

3、刻蚀\光刻机

我们常听说的那些高大尚的光刻机,是指晶圆级别上用来刻蚀芯片电路的。封装过程也要用到光刻机,需要制作用于定位和精确定位芯片的封装模板。光刻机可以用于制作这些封装模板的微米级图案。光刻机通过曝光光刻胶和进行显影的过程,将图案精确地转移到封装模板上。封装过程所用光刻机线宽要求比较低,一般500nm的都能用了。

封装用光刻机

封装用蚀刻机

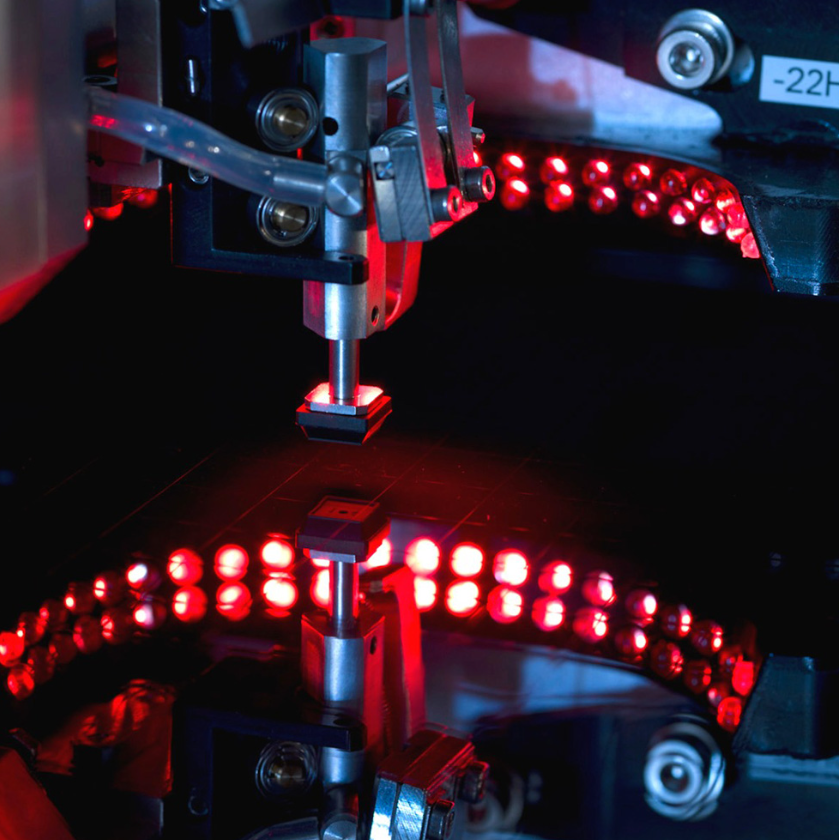

4、芯片键合机

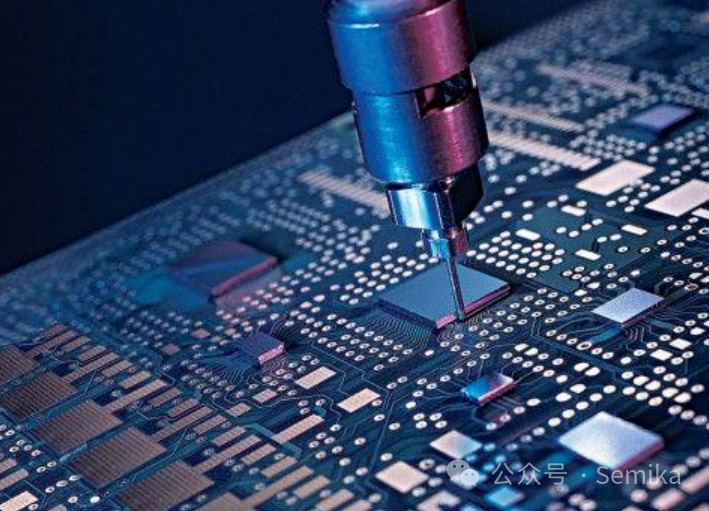

芯片键合机,是把芯片与基板连接在一起的设备,有两种主要的方式,Wire Bond和Die Bond。Wire Bond设备通常被称作绑线机,绑线机是用金属引线把IC上的引脚与基板(Substrate)的引脚进行连接的设备。这个工艺中使用的金属细线通常只有几十微米,一根一根把金属丝熔融在引脚上。这个过程在引脚多的芯片上就很耗时。Die Bond设备有时被称作贴片机或固晶机机。Die Bond是近些年才发展起来的技术,是通过金属球阵列来进行连接,就是常说的BGA技术(Ball Grid Array)。Die Bond的连接方式效率更高,一次性可以连接所有引脚,所以生产数百数千引脚的芯片也很方便。还有就是Die Bond封装更加紧凑,所以Die Bond是未来芯片键合的主要方式。

Wire bond 设备

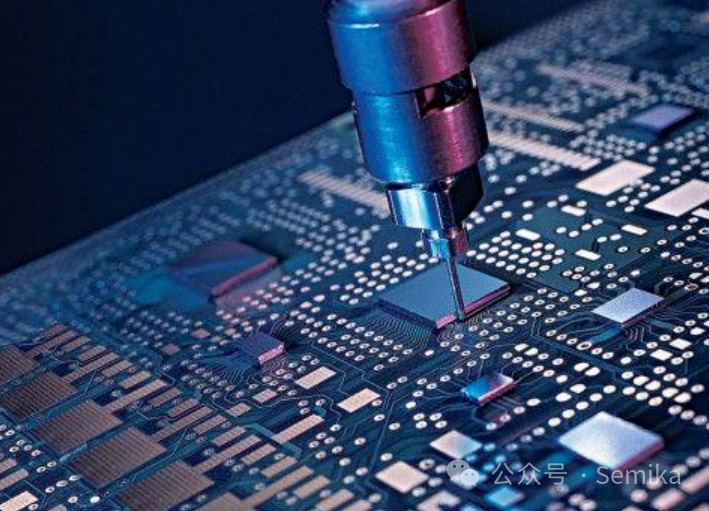

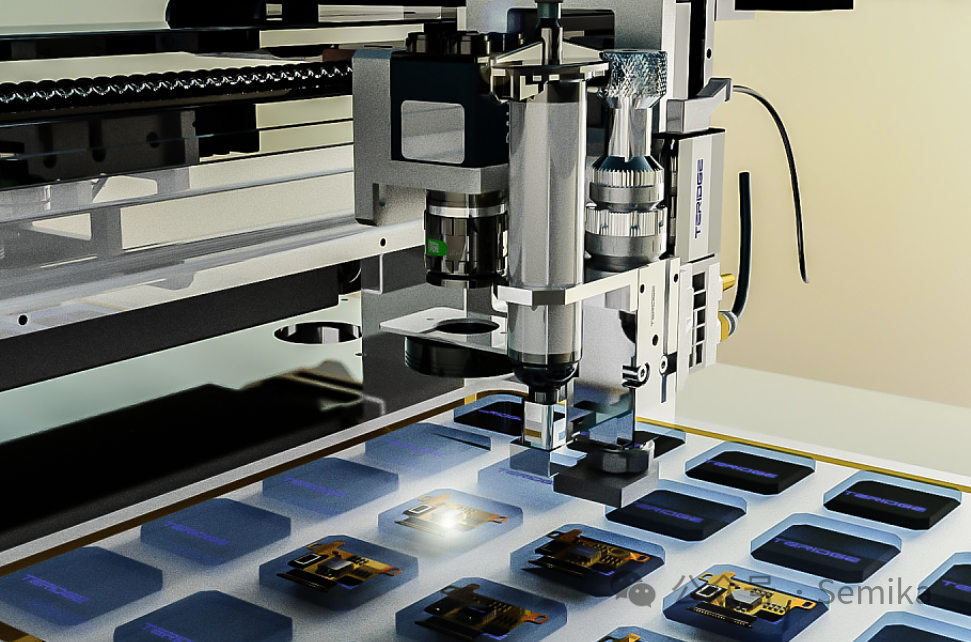

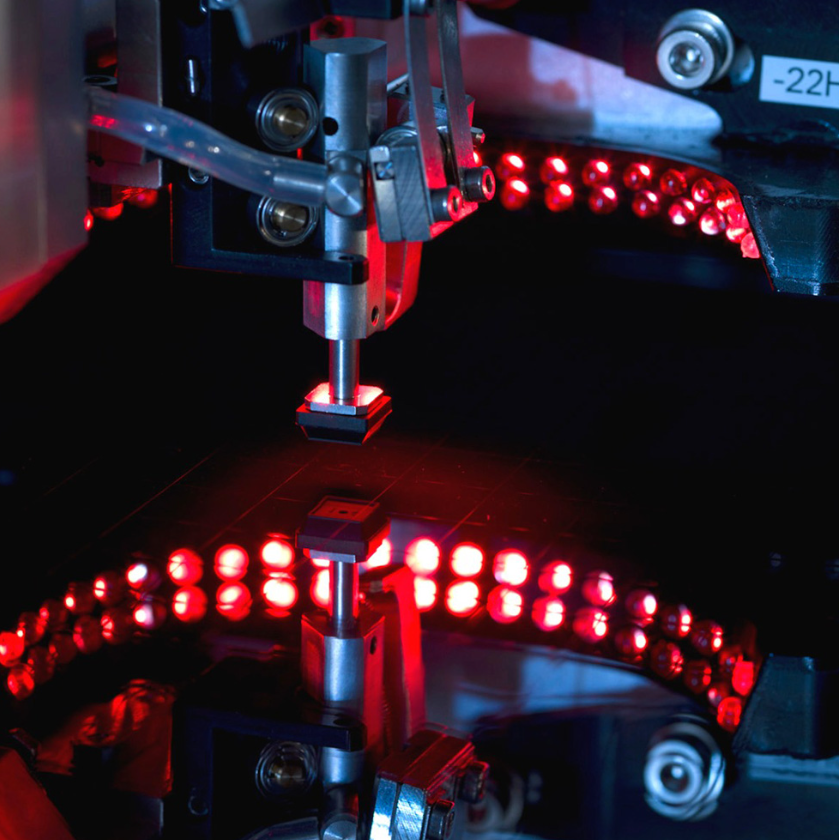

5、贴片机

贴片机是一种高度复杂且精密的机器,其工作原理可以追溯到微电子组件制造的核心。这些机器使用先进的视觉系统,如光学传感器和高分辨率摄像头,以检测和定位微小的电子元件。这种视觉系统能够在纳米级别准确度下进行操作,确保元件的精确定位。

贴片通常是指表面贴装技术,是一种将无引脚或短引线表面组装元器件(简称SMC/SMD,中文称片状元器件)安装在印制电路板(Printed Circuit Board,PCB)的表面或其它基板的表面上,通过再流焊或浸焊等方法加以焊接组装的电路装连技术。

除此之外,贴片还指应用于裸芯片(Die)的贴装技术,是指将晶圆片上没有封装或保护层的晶片(裸芯片)贴装到基板上的过程。这些芯片通常由硅等材料制成,并通过刻蚀、沉积、光刻等工艺加工而成。

裸芯片贴装是一种高精度、高技术含量的制造过程,在贴片过程中,由于裸芯片缺乏封装保护,对裸芯片的测试和组装要求更高,需要专门的贴片机设备和技术来确保其可靠性和稳定性。裸芯片贴装技术常用于高性能计算、光通信、存储和其他应用领域,其中需要更高的处理能力和集成度。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学