十多年来,半导体行业经历了摩尔定律放缓,下一个晶体管节点的成本和技术挑战急剧上升。作为回应,该行业在2.5和3D平台中采用了具有垂直堆叠的先进封装,以实现更高的计算性能,克服高级节点放缓的问题,并保持产品能够及时发布。

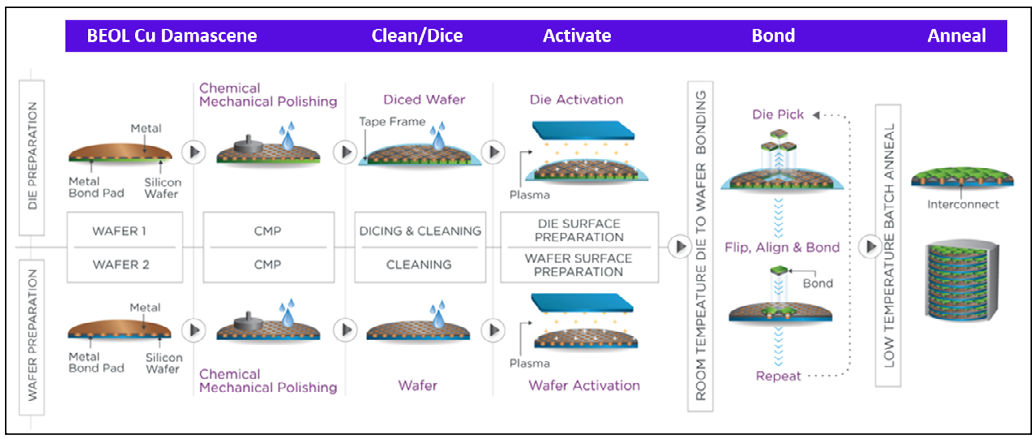

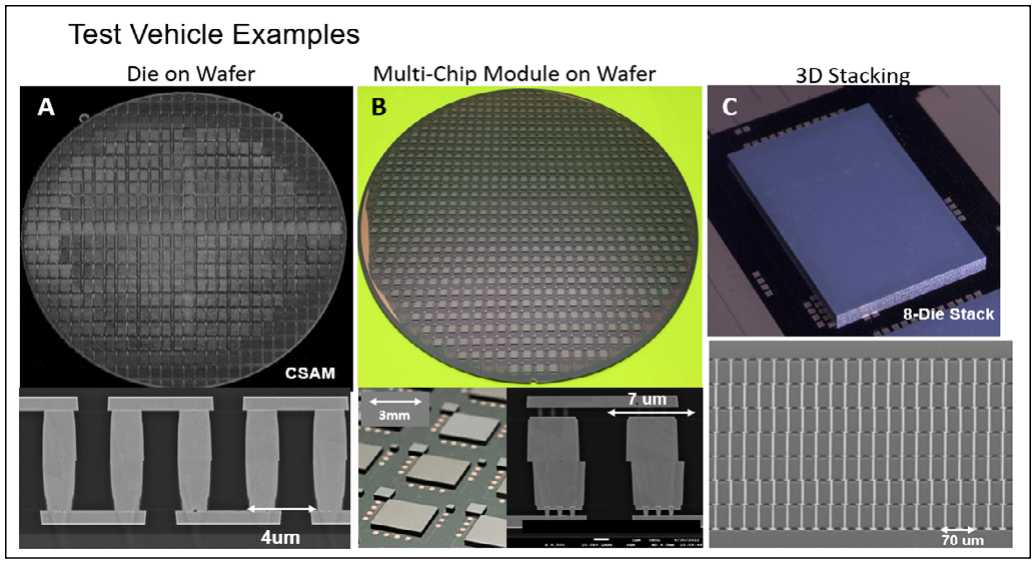

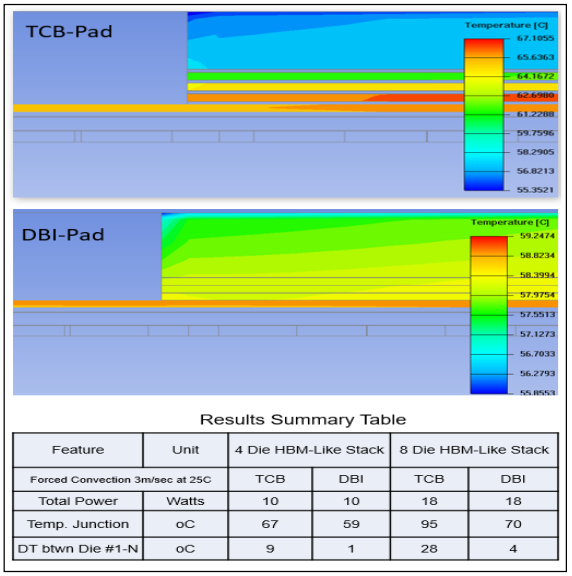

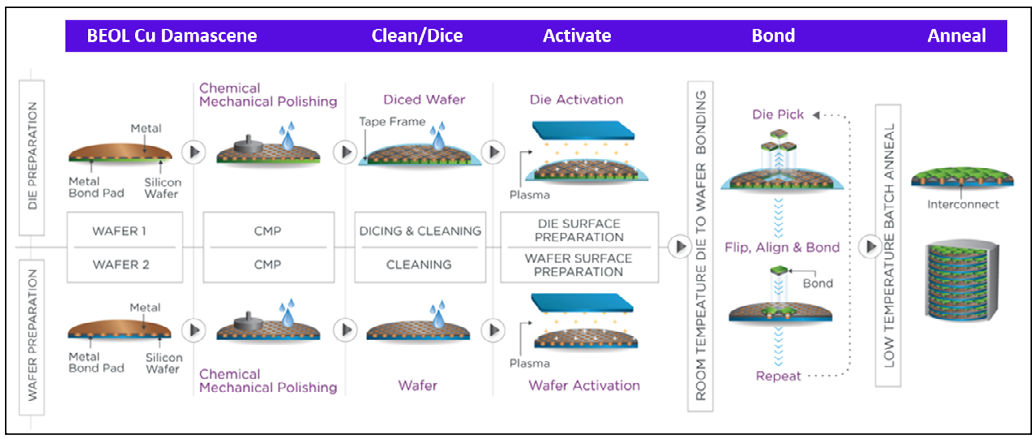

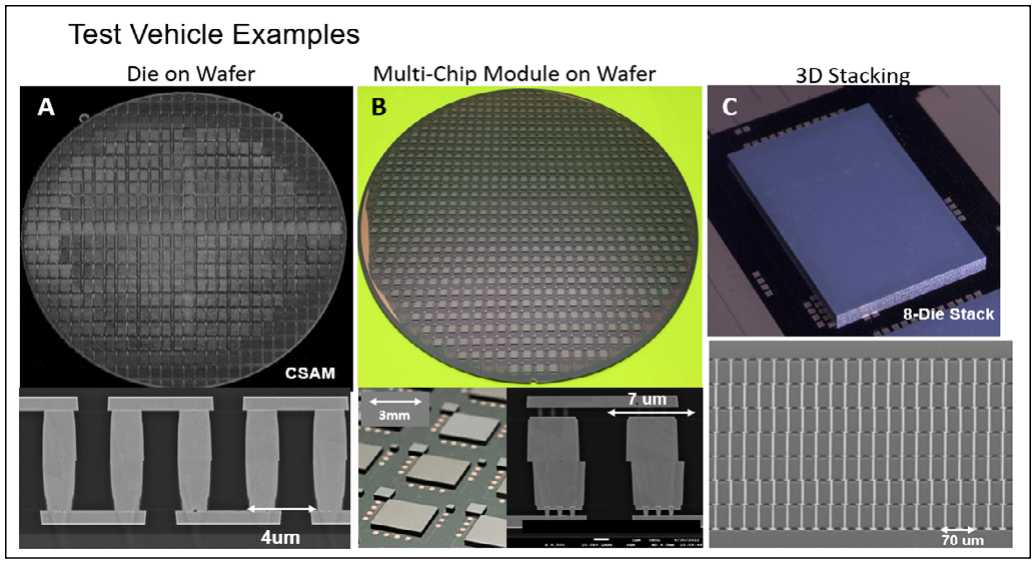

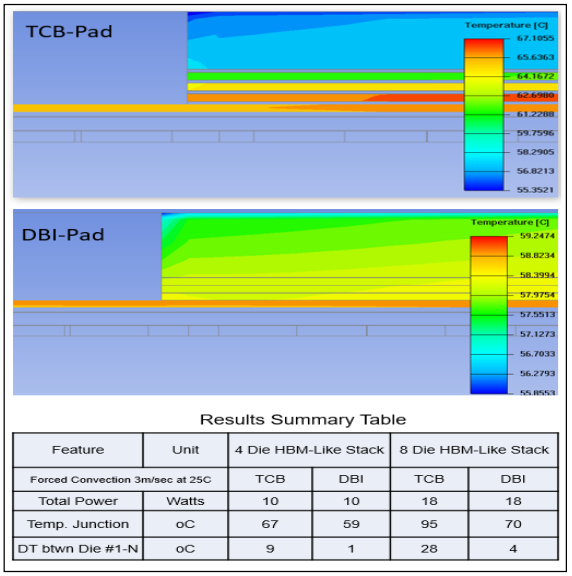

关于小芯片,使用混合键合技术可以实现更高的性能和更短的上市时间,虽然其扩散速度还有待观察,但它似乎已成为新一代混合键合封装创新的开始。SoC不适合小批量制造,10多年来,利用硅通孔(TSV)技术的基于硅中介层的2.5和3D封装已在进行大规模制造。在企业的推动下,这一生态系统逐步发展起来。这些公司将逻辑上的存储器(MoL,memory-on-logic)堆栈引入产品。2.5D中的小芯片(chiplet)的成本可以比单片结构降低一半。然而,这些产品的采用仅限于少数公司,原因是互连密度和总体成本存在技术挑战。目前,成本管理仍然是先进封装采用和扩散的中心主题。当今SoC的整体性使设计和开发成本不断上升,不能满足小批量制造商和实体的要求。特别是当通用异构集成和IP复用策略(CHIPS)计划诞生时,这一问题更加凸显。该计划的目标是创造一种范式转变,“增强整体系统灵活性,减少下一代产品的设计时间,并实现显著的IP复用。”TSV的2.5D和3D封装的技术成功和经验为新的小芯片时代的可能性奠定了激动人心的基础。小芯片是具有特定功能的集成电路(IC)的一部分,适用于与其他小芯片组合,以完成封装或系统内的全功能模块。它需要一个I/O控制器芯片来实现多个小芯片模块的组合,起到n个IC的作用。与传统SoC封装相比,其优势在于异构集成、已知合格芯片和可用于多种应用的可重用IP。新小芯片时代的价值主张是从根本上降低成本,同时为电子产品中提供增强的功能。成本管理的主题是芯片尺寸缩减、分解、缩短上市时间、标准化I/O协议和增加IP重用。创建了多个连接到基板上内存的小芯片核,显示出向分布式计算的重大转变。案例研究表明,使用分布式小芯片计算架构可以将开发成本降低8倍。由于较低的缺陷密度,较小的芯片具有较高的良率。分解对于适当地使用传统芯片的能力非常重要。例如,根据具体应用,A/D转换器更适合使用传统节点,而一些处理器更适合使用最新节点。在最有利的节点或工艺中设计和制造IC提供了更多节省成本的选择。小芯片的重复使用减少了产品系列的开发时间,并及时向市场提供差异化性能,从而降低开发成本。小芯片对IC架构师来说是个不错的选择。封装重组是集成电路面临的现实挑战,包括传统铜微泵缺乏可扩展性和性能,以及行业内各种封装方法中的非标准IP。今天的产品在25μm间距下I/O数量有限,而许多小芯片和2.5D模块将受益于存储器和逻辑或逻辑/逻辑接口之间更精细的间距互连,可以提供高带宽和低延迟,这对计算至关重要。2016年以来,晶圆到晶圆(W2W)制造中一直在采用细间距直接键合互连(DBI)混合键合,如2.5-8μm的图像传感器,最近又用于1μm左右的NAND存储器制造,制造生态系统已经准备就绪。混合键合需要一定的清洁度(ISO-5至ISO-4),类似后道工序(BEOL)晶圆制造,因此,晶圆键合工艺线有了一个直系亲属。此外,芯片到晶圆(D2W)和芯片到芯片(D2D)混合键合制造准备工作已经发展了多年。先进封装OSAT通常在ISO-7环境中运营,需要升级其基础设施,以实现混合键合先进互连技术。随着互连间距在D2W应用中继续按比例缩微,微环境清洁度规范将收紧。集群工具平台目前正在考虑提高封装厂及其他制造设施的规模和吞吐量,以引入这项新技术。过去5年,D2W键合设备的对准精度和局部环境清洁度的差距已经解决。大批量制造(HVM)工具的规格约为3μm至5μm,吞吐量约为2000个/小时。贴片设备制造商开始将他们的路线图与间距低于20μm的混合键合小芯片所需的清洁度和对准精度相匹配,一些公司还在计划亚微米贴装精度工具,以支持未来几代的间距缩微。在Ultra组装工艺中,混合键合互连是用标准BEOL Cu镶嵌工艺形成的,包括介电沉积、蚀刻、阻挡层、Cu子晶层、Cu板和化学机械抛光(CMP)。在获得300mm晶圆的纳米级形貌控制后,必须对晶圆进行切割。芯片处理是在带框上完成的。CMP之后,芯片表面必须按照清洁度规范进行划片。实践证明,所有三种切割技术(机械锯、隐形和等离子体)均具有等效性能。该过程的最后步骤是活化、键合和退火。混合键合互连的晶圆上芯片(WoD)配置示例:a)WoD;b)晶圆上多芯片模块;c)3D堆叠根据JEDEC环境应力测试标准,组装并测试了存储器逻辑接口配置中的单芯片堆叠,互连间距为40-4μm,有30k至1.6M互连。同时,4和8管芯堆叠堆叠设计有6k I/O,采用类似HBM格式,具有35μm的互连间距TSV。所实现的全Cu互连不存在金属间化合物,或导致Cu微凸块中电气故障和机械弱点的Kirkendall空洞的推动力。相反,由于键合界面上Cu-Cu扩散的增强,混合键合菊花链测试结构中的电阻略微降低。直接键合中的互连由将多个管芯固定在一起的强键合电介质包围。在功能操作期间传递到混合互连的机械应力比在Cu微凸块中小得多。混合键合互连与新的小芯片时代的路线图非常一致。用标准BEOL Cu镶嵌工艺形成的混合键合互连可通过半导体供应链进行扩展。在间距1μm及以下时,最大互连密度大于1×106互连/mm2。混合焊盘互连的小尺寸保持了低电感及信号完整性的理想电容。管芯之间更均匀的热导率可以减少热点恶化,并允许冷却方案更有效地对整个管芯堆叠产生积极影响。在4和8 DRAM配置堆栈仿真中,比较了互连的管芯1-4和管芯1-8之间的温差。混合键合堆叠中的管芯1和管芯8之间的温差(ΔT)(4℃)远低于TCB结构(28℃)。堆叠内管芯之间较低的ΔT对于具有温度敏感性能的高速器件(如DRAM)来说是一个显著的优势。减少缺陷密度导致的良率损失正在驱动新的小芯片时代的分布式计算。同样,缺陷密度成本驱动因素使行业从单片芯片转向小芯片,这对于需要洁净环境的混合键合互连技术至关重要。这种针对分布式架构的收缩组件的方法也有利于混合键合收益率的提高。管芯良率、电性能和热性能的综合增强是将3D小芯片与混合键合互连集成的有力论据。半导体行业的保守性质要求能够为增强多代产品的技术进行投资,这些技术与可扩展混合键互连的价值相得益彰。小芯片能够使用先进封装技术在更短的开发时间内实现与先进节点同等的性能,让行业对无处不在的异构集成供应链感到兴奋。虽然这种高性能互连在供应链和市场中的扩散速度仍有待观察,但这已经是新一代混合键合封装创新的开始。