终极指南:ASIC(专用集成电路)

作者:admin 来源:本站 发布时间:2021-05-25 访问量:4001

集成电路(IC),也称为芯片或微芯片,是在通常为硅的半导体材料的单个小平板(或“芯片”)上的一组电子电路。现代IC非常复杂,并且在单个芯片上包含数百万个晶体管。

根据其设计方法,灵活性和应用,可以使用不同类型的IC:

标准IC、ASIC(专用集成电路)、ASSP(专用标准产品)。

由于本文的重点是ASIC,因此我们将它们分为两类:ASIC和非ASIC。我们将在这里讨论ASIC及其类型。

ASIC简介

专用集成电路(ASIC)是为特定用途或应用而设计的非标准集成电路。ASIC通常是为将要进行大量生产的产品而设计的,并且它包含单个集成电路所需的大部分电子器件。结果,ASIC设计(例如NRE)的成本非常高,因此ASIC通常用于大批量产品。

尽管ASIC的设计成本很高,但对于许多大批量应用而言可能是具有成本效益的,特别是当大型系统的重要部分可以集成到一个ASIC电路中时,大大减少了外部组件的数量。ASIC通过减小电子产品的尺寸并增加每个芯片的逻辑门密度来帮助革新技术。ASIC的例子很少,例如Intel的CPU或比特币ASIC。ASIC设计有两种主要方法:

半定制设计、全定制设计。

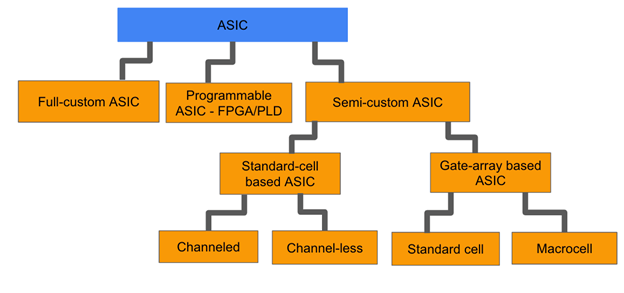

半定制设计本身分为几组。ASIC的分类如下图1所示:

图1 – ASIC的类型

有时,可编程ASIC被认为与半定制ASIC分开。ASIC还有另一种分类,区别不大,如下所示:

图2 – ASIC芯片的分类

现在,让我们简要讨论一下ASIC的不同类型。

全定制ASIC

如果是全定制ASIC,则某些或有时是所有的掩模层都是定制的。制造这种类型的ASIC通常需要8周的时间(当然,这不包括设计时间)。

仅在以下情况下才需要全定制ASIC:

没有合适的库,或者现有的库不够快、可用的预先设计的单元消耗的功率超出允许的范围、可用单元的面积太大或该技术是新技术,尚不存在任何库。

全定制ASIC具有以下优点:

制造最便宜(因为面积更小)、提供最高速度。

当然,它们也有一些缺点,如下所示:

复杂性增加、增加设计时间、设计成本较高、更高的风险。

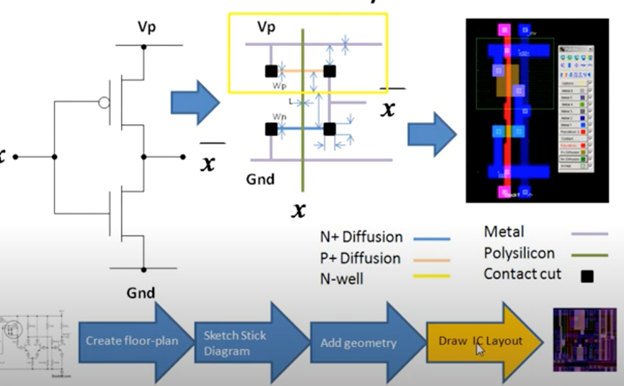

下图3显示了原理图的全定制布局的设计流程:

图3 – 全定制ASIC的布局设计流程

半定制ASIC

第一组半定制ASIC是基于标准单元的ASIC(CBIC),它们使用预先设计的逻辑单元(称为标准单元)。当我们说ASIC时,我们通常会了解这类ASIC,因为它们是最常见的。为了创建这种类型的ASIC,从以下方面使用逻辑单元:

标准单元库、巨型电池(例如,微控制器或微处理器)、全定制模块、系统级宏(SLM)、功能标准块(FSB)、核心等。

NAND2X1标准单元的布局如图4所示。

图4 – NAND2X1标准单元布局

基于半定制标准单元的ASIC设计中使用的库的标准单元是使用完全定制设计方法构建的。它们确保相同的性能和灵活性,但减少了时间和风险。因此,ASIC设计人员仅在基于S Standard-Cell的ASIC设计期间定义标准单元的放置。

CBIC中的柔性块的构造遵循以下原则:

标准单元的建造就像墙上的小砖块一样、标准单元格水平放置以形成行、通过在垂直方向上堆叠行来构建柔性块-在设计期间进行重塑、柔性块与其他标准单元块或完全自定义块连接。

在这种类型的半定制ASIC(CBIC)中,所有的掩模层(晶体管和互连)都是定制的。制造过程通常需要8周的时间。在这种类型的ASIC中,可以嵌入自定义模块。与其他类型的ASIC一样,它们都有优点和缺点。一些优势如下所示:

节省时间,金钱并降低风险、可以针对面积,功率或速度分别对标准单元进行优化。

这种ASIC的一些缺点是:

设计标准单元库需要花费大量时间和金钱、增加用于新设计的芯片所有层的制造时间。

基于门阵列的ASIC

在基于门阵列的ASIC中,晶体管是在硅晶片上设计和制造的,但是没有制造互连。基本阵列是门阵列上晶体管的预定义图案。

重复形成门阵列的最小元素称为基本单元。设计人员可以使用自定义掩膜来定义仅用于定义晶体管之间互连的金属互连的最顶层。通常将其称为屏蔽门阵列(MGA)。这种类型的ASIC的周转时间较短:通常从几天到几周。

门阵列,屏蔽门阵列或预定义门阵列使用书本(微距)来减少周转时间,并包括由其制成的基础阵列。基本单元或基本单元。有三种类型的门阵列:

通道门阵列、无通道门阵列、结构化门阵列。

通道门阵列

仅在通道门阵列中,互连是自定义的,并在基本单元行之间使用预定义的空间。制造提前期需要2天到2周的时间。这与CBIC非常相似,但是与CBIC相比,此处的空间是固定的。

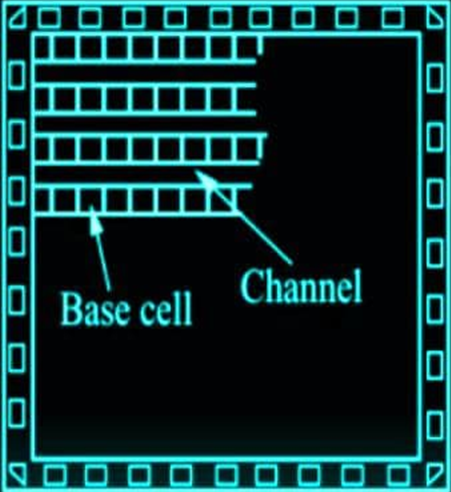

在无通道门阵列(也称为无通道门阵列),门海阵列或SOG阵列中,仅定制了一些(顶层)掩模层(互连)。制造提前期需要2天到2周的时间。通道门阵列ASIC的高级架构如图5所示:

图5-通道门阵列ASIC的架构

通道门阵列的最大优点是存在互连的特定空间。

这种阵列的最大缺点是,例如,与CBIC相比,无法调整空间。

无通道门阵列

无通道门阵列和通道门阵列之间的主要区别:

没有预留用于在无通道门阵列上的单元之间进行路由的预定义区域。

使用晶体管区域在无通道阵列中进行布线时,我们不会与位于其下方的设备建立任何接触。

对于无通道门阵列,在给定的硅区域中可以实现的逻辑量更高。

在无通道门阵列中,连接掩模是自定义的,但通常在通道门阵列中不是自定义的。这导致无通道架构中的单元密度更高。

在无通道门阵列中,自定义接触层可以提高门阵列单元的密度,因为我们可以在未使用的接触部位上方布线。

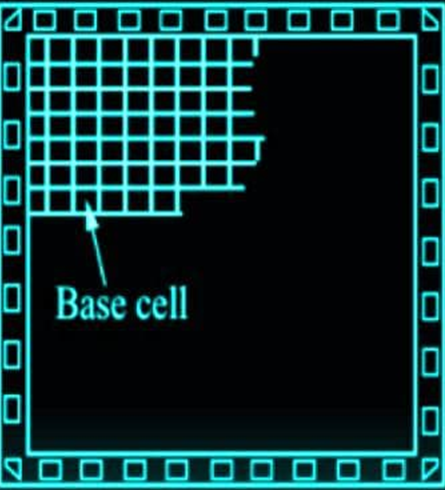

图6显示了这种类型的ASIC的高级体系结构:

图6 – 无通道门阵列ASIC的架构

无通道门阵列的优点在于:

逻辑密度更高、接触层是定制的。

主要缺点是:

没有特定的路由区域、用于布线的晶体管行不能用于其他目的。

结构化门阵列

结构化门阵列结合了CBIC和MGA的某些功能。

MGA的最大缺点之一是固定门阵列基本单元。例如,这使得存储器的实现效率低下或困难。

在结构化门阵列(也称为嵌入式门阵列),母片或主映像中,仅互连是定制的,定制块(每种设计相同)可以被嵌入,制造过程可能需要两天到两周的时间。

在嵌入式门阵列中,一些IC区域被留出并专用于特定功能。

该嵌入式区域可以包含:

更适合用于构建存储单元的其他基本单元,或者可以包含一个微控制器或另一个完整的电路块。

图7显示了结构化门阵列ASIC的高级体系结构:

图7-结构化门阵列ASIC的架构

结构化门阵列的主要优点是它们设置在某些IC区域中,专门用于定制的特定功能、提高区域效率,提高CBIC的绩效、低成本和MGA快速周转。

最大的缺点是嵌入式功能是固定的。

可编程ASIC

可编程ASIC是ASIC的一种,可以在制造后在硬件级别进行编程。

一些可编程的ASIC:

PLD:它们仅包含1k-10 k门的低密度器件

FPGA(CPLD或FPLD)是可编程ASIC,将门阵列的架构与PLD的可编程性结合在一起。PLD没有定制的掩模层或逻辑单元,因此可以快速进行设计周转。可以对PLD进行配置或编程,以创建针对特定应用定制的零件。

PLD的一些示例是ROM,PROM,EPROM。

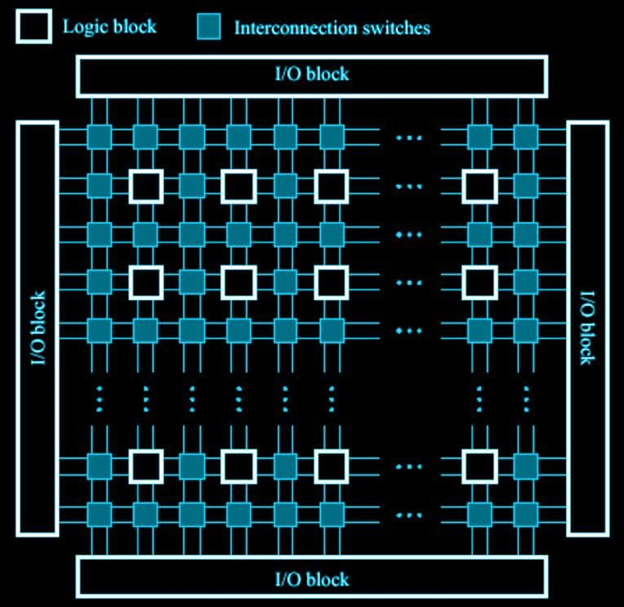

与PLD相比,FPGA更大,可用于更复杂的应用。FPGA IC的架构如图8所示:

图8 – FPGA的架构

以下是FPGA的一些主要功能:

FPGA内部的可编程基础逻辑单元的核心-常规数组实现组合或顺序逻辑、可编程互连矩阵围绕基本逻辑单元、可编程I / O单元围绕核心、使用了一种对基本逻辑单元和互连进行编程的方法,它没有定制的遮罩层,它的设计周转时间为几个小时。

可以根据以下因素决定是否使用FPGA:

速度、数据流、门密度、开发时间、原型制作和仿真时间、制造提前期、是否需要将来修改、库存风险、成本。

上一篇:安全加固:芯片设计环境的防护线

下一篇:IC故障排除和IC故障分析

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学