CXL 仲裁器和多路复用器概述

作者:admin 来源:本站 发布时间:2021-06-08 访问量:4657

CXL 是一种用于加速器、GPU 等高带宽设备的有抱负的新技术。在对高性能计算 (HPC) 需求不断增长的时代,CXL 提供主机(通常为 CPU)和主机之间的高带宽和低延迟连接。加速器、内存扩展设备等设备。

CXL 利用现有的 PCIe 5.0 物理层基础设施和 PCIe 备用协议协商过程,并增加了一些改进,以支持来自多个协议的数据传输。

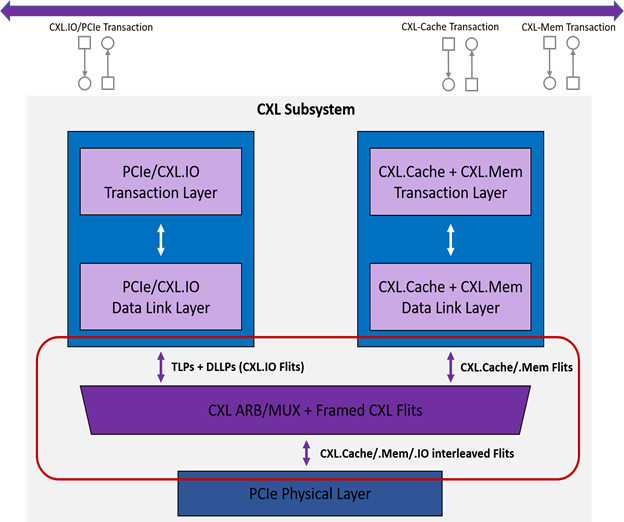

CXL 引入了一个新组件Arbitrator 和 Multiplexer,以促进传统 PCIe 物理层的使用。Arb-Mux 动态复用来自多个协议(CXL.IO 和 CXL.Cache-Mem)的数据并将其路由到物理层。这种方法有助于行业过渡并利用 CXL 支持的新功能,而无需在物理层中进行许多更新,这是设计中最复杂的组件之一。

显示 Arb-Mux 在 CXL 堆栈中的位置的片段

以下是 Arb – Mux 的一些显着特点:

用于与多个链路层共享同一物理层。

能够复用来自多个协议的流量。

提供 CXL.IO 和 CXL.Cache-Mem 迁移的仲裁 (Tx) 和数据控制 (Rx)。

如果要在仅 PCIe 模式下访问链路,则支持 Arb-Mux 旁路功能。

虚拟链路状态机 (vLSM) 帮助每一层与链路状态同步。

每个链路层的虚拟化 Active/PM 状态,允许一个协议处于 PM 状态而另一个协议处于活动状态。

状态同步以在多个 LTSSM 过渡到恢复期间保持握手稳健。

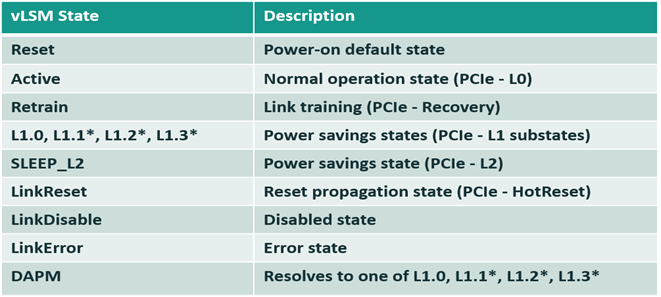

虚拟链路状态机(vLSM):

为各个 CXL 链路层维护虚拟链路状态机 (vLSM)。

通过链路管理数据包 (ALMP) 与远程 Arb/Mux 协调状态转换 [在 Tx 上馈入仲裁器,并在 Rx 上消耗]

确定 Flex 总线物理层的链路状态请求。

随着 CXL 2.0 的引入,对于 Arb – Mux 链接来操作 CXL.IO 是最低要求。

以下是 vLSM 状态及其相应 LTSSM 状态(如果适用)的概述。

有关所有 vLSM 状态转换的详细说明,请访问 CXL 2.0 基本规范。

ARB – MUX 链路管理包 (ALMP):

ARB – MUX 使用 ALMP 来传达虚拟链路状态转换请求和状态。

ALMP 是一个 1 DW 数据包,并在 528 位 flit 的低 16 字节上复制 4 次以提供数据完整性保护。

可以分为两类:

请求 ALMP,用于启动 vLSM Active/PM 状态转换。

状态状态 ALMP,用于将当前状态传达给远程伙伴。

任何 ALMP 错误或收到意外 ALMP,都会导致 LTSSM 转换到恢复。

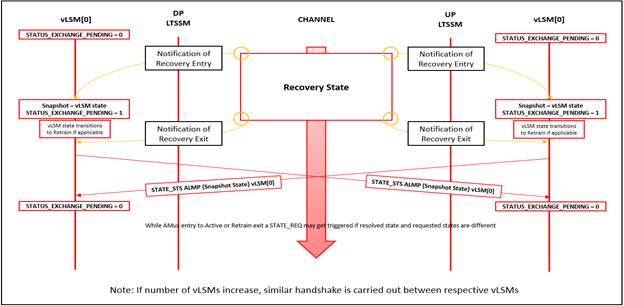

阿尔普握手:

由于 PM 和 Active 是虚拟化状态,遵循 ALMP 握手可确保 Tx 和 Rx 与远程伙伴 vLSM 状态同步。

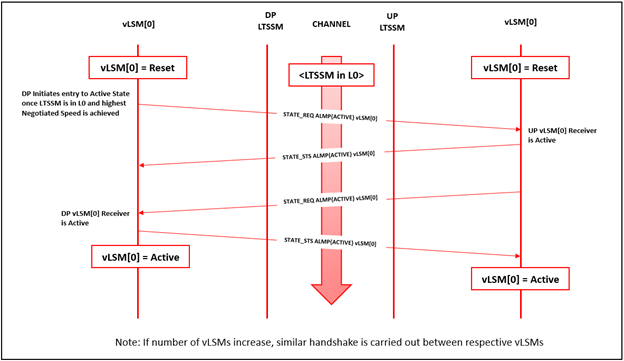

进入/过渡到活动状态:

首次进入 Active 仅由 DP 启动,后续转换可由 DP 或 UP 启动。

需要从双方发送和接收 Active Request ALMP。

一旦端口准备好接收flit,就会返回活动状态ALMP。

在两个端口 vLSM 都移动到 Active 之前,在链路上看到的两对 Active Request 和 State Status ALMP(一对用于 DP 请求到 UP,反之亦然)

显示进入活动状态的片段

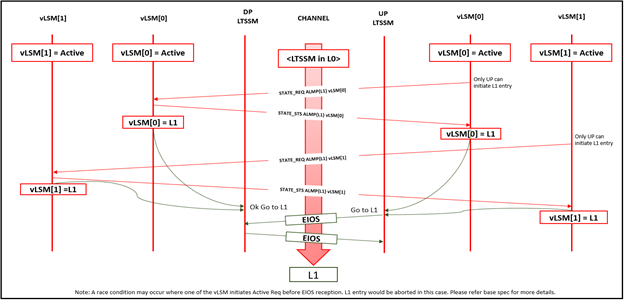

转换到 L1.x 状态:

只能由 UP 发起,通过发送 PM 请求 ALMP。

如果 DP 准备好转换,它会将 vLSM 转换为请求的 PM 状态并以 PM 状态状态 ALMP 响应。

UP 可以在收到 PM 状态状态 ALMP 后转换 vLSM。

显示进入 L1 PM 状态的片段

状态同步协议:

需要在 LTSSM 的恢复转换中保持握手的稳健性。

物理层退出后,需要从每个 vLSM(DP 和 UP)发送状态 ALMP 恢复(在传输链路层迁移之前需要)

传输状态状态 ALMP 中指示的状态是 vLSM 状态的快照(快照状态:LTSSM 退出恢复后的 vLSM 状态)

基于同步交换期间发送和接收的状态 ALMP 的相应状态状态解析(如果解析状态不等于链路层请求状态,则新状态请求和状态 ALMP 交换)

显示 LTSSM 从 Recovery 退出期间状态交换的片段

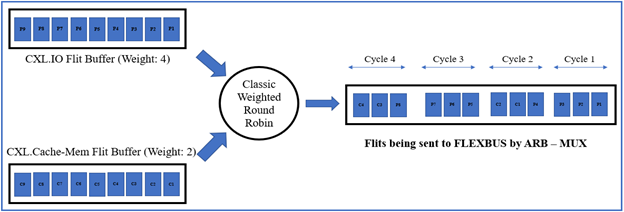

仲裁政策:

Arb – Mux 提供 CXL.IO 和 CXL.Cache-Mem 迁移的仲裁 (Tx) 和数据控制 (Rx)。

仲裁策略是具有指定寄存器的加权循环,以分别对与 CXL.IO 或 CXL.Cache-Mem 相关联的相对权重进行编程。CXL 2.0 存储器映射寄存器包含定义变量以控制此权重的 Arb – Mux 寄存器。

下面的图示显示了 Arb – Mux 如何使用加权循环 (WRR) 方法仲裁 IO 和 Cache-Mem 迁移。

显示加权循环 (WRR) 仲裁策略的片段

我们有 2 个缓冲区,CXL.IO flit Buffer 和 CXL.Cache-Mem flit Buffer。考虑两个缓冲区都已满的情况。截至目前, CXL.IO 的权重设置为4, CXL.Cache-Mem的权重设置为2。这意味着 CXL.IO 的 4 次飞行将跟随 CXL.Cache – Mem 的 2 次飞行。

与经典WRR的方法中,1日周期将调度来自CXL.IO微片缓冲器即,第一微片3 P1,P2和P3。在第二个周期中,来自 IO 缓冲区即P4 的1 次迁移,因为 CXL.IO 权重为 4,其余 2 次迁移将来自 Cache-Mem 缓冲区,即C1和C2。同样,将针对缓冲区中剩余的可用迁移进行仲裁。

如果任何一个缓冲区为空,Arb – Mux 将自动处理仅从非空缓冲区发送 flit。

验证挑战:

由于 Arb – Mux 夹在多个链路层和现有物理层之间,因此该组件的无错误实现具有重大责任。

以下是 eInfochips 在 Arb – Mux 验证期间解决的一些挑战:

建立初始流量:作为第一个验证 CXL 和 Arb – Mux 设计的团队,Verification 的一个主要痛点是初始流量。由于 Arb – Mux 是一个相对较新的代码,因此验证流量成为一个关键项目。

传输接口:基本上,有两种类型的接口与 Arb – Mux 相关。

链路层和 Arb – 多路复用器。

Arb – 多路复用器和物理层

数据接口和控制接口之间:

最重要的是,这些数据传输接口在物理层和链路层之间路由有效数据,反之亦然。

来自物理层的背压(物理传输操作系统)

LTSSM 进入/退出 Recovery。

链路和物理层转换到 PM 状态。

还有很多。

状态同步:Arb – Mux vLSM 状态的正确交换应该发生,因为是 Arb – Mux 将物理链路的状态传达给上层。

数据仲裁和多路复用:Arb – Mux 永远不应优先考虑仅来自一种协议的数据。如上所述,数据仲裁策略是一个加权循环。此外,在从 Arb – Mux 向链路层发送数据时,应将其路由到有效通道。例如:将 CXL.IO flit 路由到 CXL.IO 链路层并将 CXL.Cache-Mem flit 路由到 CXL.Cache-Mem 链路层。

挑战不仅限于上面列出的项目。我们处于一个充满惊喜的领域,我们面临着多个运行时障碍,有时难以用语言表达。

处理验证瓶颈:

熟练地处理上述验证挑战和瓶颈需要努力工作、毅力和短暂的技术专长。下面列出的属性展示了我们作为一个团队如何能够应对这些挑战。

超过 15 年的 PCIe 专业知识:由于 CXL 建立在与 PCIe 类似的线路上,因此 PCIe 协议的知识/专业知识在 CXL 验证中也起着至关重要的作用。

适应新技术:VLSI是一个竞争激烈的行业;对于客户来说,将他们的产品推向市场是一场与时间的赛跑。快速适应新技术,帮助我们有效地满足客户的这一要求和许多其他要求。

根本原因设计失败:通过根本原因导致设计失败来帮助设计师。这涉及在 RTL 或源代码中精确定位设计缺陷。

上述指针不仅限于我们,其他团队也可以使用它,这可以帮助他们将Arb – Mux 和CXL Verification 作为一个整体进行准备。

结论

VLSI 是一个不断发展的行业。在未来的时间里,它将看到类似的技术进步。自过去二十年以来,eInfochips 确保采用所有这些新技术,并通过为客户提供具体的解决方案和支持来有效地满足他们的期望。CXL 只是皇冠上的另一根羽毛。

关于作者

Vinit Sheth

Vinit Sheth 在 eInfochips 担任 ASIC 设计验证工程师。他在验证领域有 3 年的工作经验,曾研究过一些复杂的协议,如 CXL、PCIe、CCIX 和 USB。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学