地理空间异常值检测

作者:admin 来源:本站 发布时间:2021-08-06 访问量:2880

将芯片测试结果与晶圆上的其他芯片进行比较有助于识别异常值,但将这些数据与异常值的确切位置相结合,可以更深入地了解可能出错的原因和原因。

异常值检测的主要思想是在晶片中或晶片上找到与晶片上所有其他晶片不同的东西。借助最先进的良率和测试管理数据分析平台,在芯片邻居的环境中执行此操作变得更加容易,但它仍然会变得复杂。甚至邻居的定义也可能有所不同。

一段时间以来,晶圆空间变化已被用于识别和破译良率问题,但主要用于现场故障的事后分析。产品和质量工程师越来越多地应用这种通过/失败测试决策,尤其是在安全关键或任务关键应用中,因为基于部件平均测试 (PAT) 的简单异常值检测技术缺乏有效平衡良率/质量/成本三角的本地化.

PAT 以外的技术依赖于多次测量、对测试结果的算术运算以关注通过/失败区分以及地理空间关系。但是地理位置和相关的测试结果也需要额外的工程资源,因此在高级节点和质量和可靠性至关重要的应用中,成本正在上升。

“每次在技术上进行重大转变时——例如铝铜互连和传统的高 K 金属栅极——都会出现一系列你以前从未见过的新事物,”Ken Butler 说, Advantest America 的战略业务创建经理。“随着每一次重大的技术转变和更小的几何形状,越来越有必要摆脱简单的统计数据,因为他们不再削减它了。”

受识别下游故障的启发,产品工程师在晶圆测试中寻求基于异常值的检测技术来筛选老化故障。在为测试逃逸开发屏幕时,他们自然而然地转向了这些异常值检测技术。这是汽车芯片制造商的标准做法,他们始终如一地应用异常值测试技术,而且他们经常开创新方法。现在,其他行业部门正在采用更主动的方法来处理异常值检测技术。

“虽然异常检测可能是遏制测试逃逸的有效措施,但我们看到更多客户在产品生命周期的早期将异常检测设计到他们的测试过程中,以在许多细分市场实现更高的出厂质量——不仅仅是汽车、医疗和航空航天,” PDF Solutions 的 Exensio 解决方案总监 Greg Prewitt 说。

芯片位置:x、y 和 z

使用地理空间异常值检测技术,在晶圆测试之后进行分析,因为在做出通过/失败决定时都需要考虑芯片及其相邻芯片的测试结果。这需要执行额外的计算,并且良率/测试数据分析解决方案支持这些计算。它可能是 IDM 自己的系统,也可能是 IDM、代工厂或无晶圆厂公司将使用的第三方解决方案。根据特定的技术,定义的邻域会有所不同。通常,这些具有直观意义。但在先进的 CMOS 工艺节点上,“邻居”的定义可能会变得复杂,这需要对“邻居”进行更微妙的定义。

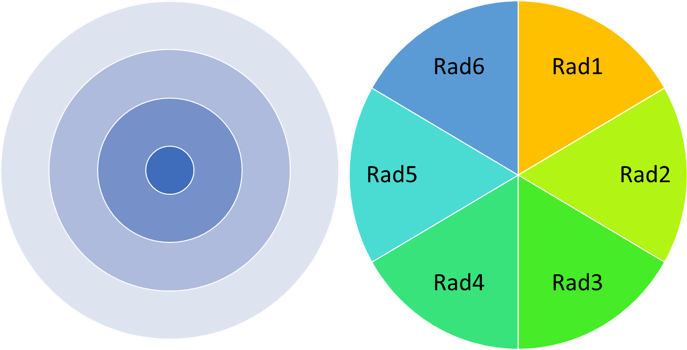

尽管业界努力在晶圆上实现统一的设备处理,但半导体制造工艺的性质产生了反映在多个制造指标中的地理模式。边缘芯片的良率低于晶圆中心的芯片。光刻胶的旋转导致径向区域。在光刻过程中,多芯片掩模版中所有芯片的焦点可能会出现细微的不均匀。

使用更小的特征尺寸,这些微妙的影响更容易表现出来,并在晶圆测试和随后的制造步骤中出现故障模具。工程师现在使用这些模式来做出有关设备通过/失败的决策。

图 1:晶片上的同心圆和放射状图案。资料来源:半导体工程/Anne Meixner

在缺陷器件的测试中,缺陷通常分为随机缺陷和系统缺陷。半导体工艺的地理性质和缺陷密度管理的增加已将重点转移到系统性缺陷上,晶圆上的地理空间关系和制造工艺发挥了作用。

Synopsys 硅生命周期管理研发总监 Dirk de Vries 表示:“总的来说,这些缺陷来源几乎从未以真正随机的方式出现。“因此,制造过程中存在工艺差异,几乎所有事物都有空间梯度。对于诸如层厚度或线宽之类的参数属性而言,情况确实如此。它们通常在晶圆上具有相当平滑的梯度,这意味着测得的芯片特性将对晶圆上相邻芯片的特性具有一定水平的预测值。你可以说,'是的,但他们有随机缺陷,随机没有预测价值。事情并没有那么简单,因为如果您查看晶圆制造缺陷,就会发现产生这些缺陷的机制。例如,它可能从晶圆边缘剥落,或在等离子体源中。关键是存在缺陷的来源,而且它们几乎从未以真正随机的方式出现。”

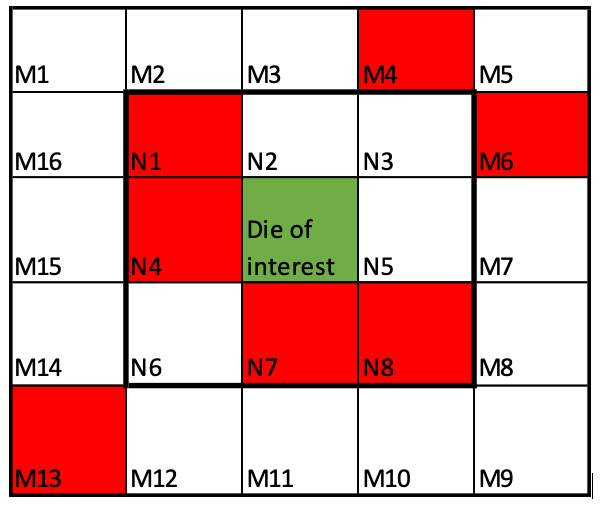

可以在数据分析平台中查看地理模式,它们可用于产量管理以识别有问题的工具或工具组合。英特尔工程师(1999 年至 2005 年)进行的一系列工程研究使用晶圆测试数据、xy 位置和电子芯片识别 (ECID) 来研究晶圆与可靠性缺陷密度之间的关系。拥有 ECID 有助于跨多个测试步骤进行数据分析。这使他们能够在芯片的晶圆测试结果中找到与批次、晶圆、xy 位置和局部区域及其邻居以及老化过程后最终测试中芯片的后续行为相关的不同模式。对于本地区域(又名邻域),他们查看了 5 x 5 区域内的芯片,并计算了标记为 N、D、T 的芯片的产量数字。

图 2:基于 xy 位置和 N、D、T 位置确定的邻域。资料来源:半导体工程/Anne Meixner

在他们的分析中,英特尔工程师指出,晶圆间差异是批次间差异的两倍。“事实证明,可追溯性是一种强大的工具,”他们指出,“用于揭示此类故障的晶圆模式中的特征。对于隐藏在生产老化数据中的细微信号尤其如此。故障分析表明,这些亚群总是因新的系统故障模式或缺陷分布而不同。”

1999 年观察到,这种本地化水平说明了 0.25 微米 CMOS 工艺的复杂性。使用当今先进的工艺节点,这些系统故障有所增加。

基于邻域

定位的异常值检测算法通过这些基于骰子与其邻居的地理空间关系的异常值检测技术而变得更小。径向位置会影响缺陷率,从而影响产量。对于测试决策的定位,邻域的概念占主导地位。接下来是查看 z 方向内的关系。

将动态 PAT 定位到更小的邻域,例如 5 x 5 或 7 x 7,使工程师能够检测这些系统故障模式的细微差异。通过这样做,工程师可以降低误报/误报。

有两种方法可以将芯片与其邻居进行比较——好芯片在坏邻域 (GDBN),坏芯片在好邻域。在过去的二十年里,包括 LSI Logic、英特尔和 TI 在内的多家公司的工程师发表了案例研究,证明这些看似严厉的决定是合理的。

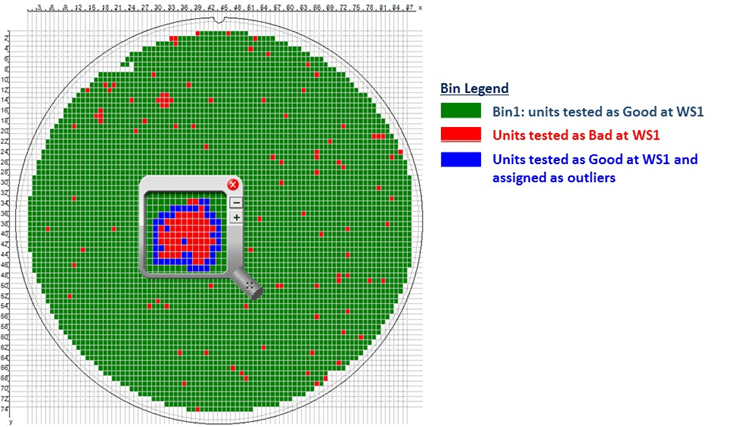

图 3:基于 xy 位置的坏邻域中的好芯片。资料来源:半导体工程/Anne Meixner

GDBN 是直截了当的,如果一个裸片通过了所有测试,但它的一些邻居被标记为坏的,那么好的裸片现在就被怀疑了。它们可以被指定为异常值,然后在晶圆分类时失败,或者被标记以进行其他良好管芯可能无法接收的额外测试。

图 4:坏社区中的好死。资料来源: 国家仪器

在好社区坏死是一个令人困惑的术语。从技术上讲,如果它通过了,它不是一个坏的模具,但它的参数不同。

“越来越多的客户试图获得更高水平的质量,因此他们正在寻找与芯片相邻的异常值。yieldHUB 的收益管理专家 Carl Moore 说:“当您查看周围的所有芯片时,预计它们在参数上是相似的。” “但有时芯片的参数测量值可能会偏离几个 sigma,可能仍在整体分布范围内。'有些东西是不对的,因为它对周围的一切都显示出不同的参数值。'”

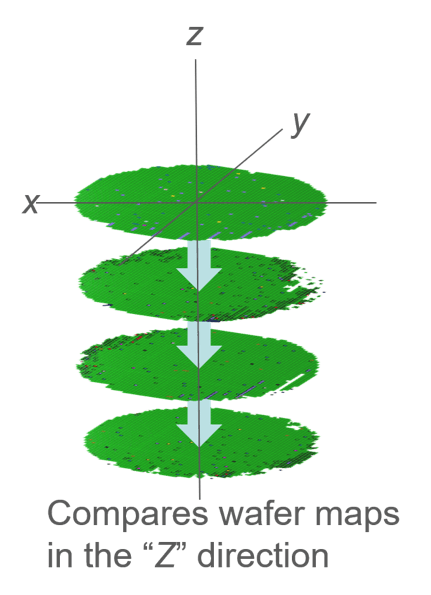

除了在 x 和 y 方向上查看邻域外,产品工程师还可以查看所有晶圆上的特定芯片位置。“还有诸如 ZPAT 之类的方法,您可以在其中对一组晶片进行 z 轴分析。这对于查找掩模中的缺陷非常有用,其中单个芯片可能总是失败或成为异常值,”摩尔说。

图 5:堆叠的多个晶圆图和 Z 方向上的故障。资料来源:银河半导体

有缺陷的掩模对良率的影响似乎很明显。参数异常值应用程序基于 25 个芯片(通常每批次 25 个晶片)的样本大小进行本地化。请注意,xy 方向上的 5 x 5 邻域也有 25 个骰子来寻找异常值。基本上,您正在堆叠晶片并在 z 方向寻找图案。

“我们早在 2005 年就在市场上推出了 Z-PAT,”Galaxy Semiconductor 的首席执行官 Wes Smith 说。“它是为一家欧洲一级汽车供应商开发的。这家公司有兴趣探索传统(即使当时)DPAT 之外的异常技术,他们正在研究各种地理空间关系,其中包括 Z-PAT。”

定义电气邻居

所讨论的地理空间技术严格考虑了物理关系。然而,即使在 20 年前,开创这些技术的工程团队也认识到 CMOS 半导体制造的系统性会影响邻域的定义。他们建议根据电气测试数据选择一个社区,而不是进行物理社区。

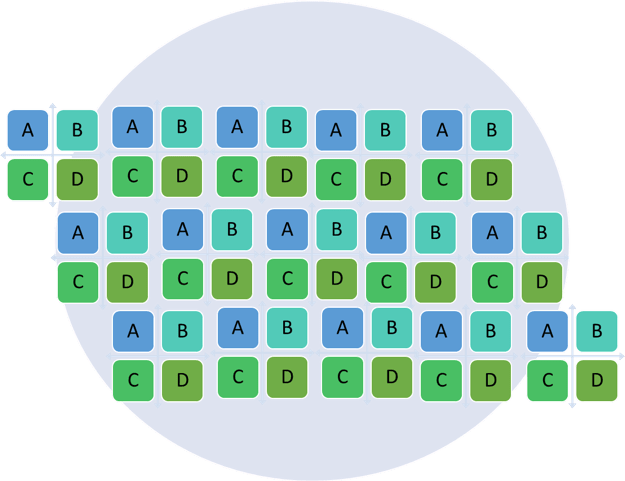

“当数据模式平滑变化时,固定的邻域选择,例如位置 x、y 的八个芯片柜在实践中效果很好,”来自波特兰州立大学和 LSI Logic 的一个工程团队在 2001 年国际测试会议论文中写道。“已经多次观察到平滑的轮廓。然而,也观察到了步进模式,它们不是平滑的而是系统的。它们在整个晶圆上施加了棋盘效应,”

图 6:步进模式棋盘效果。资料来源:半导体工程/Anne Meixner

在 IDDQ 测试中认识到这种模式后,该团队建议使用数据驱动的方法来定义邻域和要应用的限制,他们称之为位置平均。他们用 IDDQ 测量说明了它的有效性。他们的技术还包括使用测量的残差。最近邻残差 (NNR) 将地理空间关系与测试参数的算术修改相结合。NNR 本质上定义了基于相似值分布的邻域,并且该分布不是原始测试测量值。

芯片参数性能的另一个数据源是芯片上的测量,这些也可用于定义芯片内的电气邻域。这使得邻里的细化成为可能。

proteanTecs 测试和分析副总裁 Alex Burlak 表示:“为了使地理空间技术有效,需要对 xy 和 z 方向的过程变化进行强有力的假设。“在先进的工艺节点中,芯片内的工艺变化可能会很显着,并且会在 IC(邻域)或晶圆(z 方向)之间进一步增强,从而降低地理空间技术的效率。因此,更有效的技术是为每个芯片创建一个预期的基线(即采用“个性化医疗”方法),使用机器学习和高级分析技术应用于由片上通用芯片遥测 (UCT) 监视器生成的参数数据。您可以将其视为每个芯片的 PAT,而不是批次、晶圆、邻域。”

结论

在过去十年中,更广泛的产品工程社区采用基于晶片位置的测试屏幕的情况显着增加。第三方良率/测试管理系统的可用性有助于无晶圆厂和小型 IDM 使用此类技术。

“半导体行业一直强调设备质量和可靠性的重要性,”Onto Innovation 销售和客户解决方案总监 Prasad Bachiraju 说。“具有供应链集成基础设施的分析平台使晶圆厂能够根据最终测试数据执行规则和统计芯片分箱。利用与源晶圆相关的晶圆环境和芯片附近,有助于检测测试逃逸并提高芯片的整体可靠性。”

基于地理空间的异常值检测技术使工程师能够本地化“这些事物中的一个与其他事物不同”的游戏。

“你有一组你希望所有芯片都满足的性能目标,例如 100 微安的泄漏。但由于空间变化,它们并不总是达到目标,”Advantest 的巴特勒说。“所以,在测试中你会问'它们什么时候不同,它们与附近的模具有多大不同?' 我们正在谈论的所有这些技术都以晶圆位置上下文为前提。这就是为什么它们工作得这么好。”

上一篇:降低AI能耗的11种方法

下一篇:IC 测试期间的清理

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学