IC 测试期间的清理

作者:admin 来源:本站 发布时间:2021-08-20 访问量:1587

测试是一件肮脏的事情。它会污染单元或晶片,或测试硬件,进而可能导致现场出现问题。

虽然这并没有被忽视,特别是随着引脚和焊球密度的增加导致成本上升,以及随着更多的芯片被捆绑在一个封装中,灰尘的成本仍然是一个焦点。测试接口板的清洁配方正在发生变化,分析正在改进以在测试期间发现问题并提高整体设备效率 (OEE)。

通常情况下,探头和插座清理属于维护的范畴,但它比听起来要复杂得多,影响也更大。这些操作会影响 IC 的可靠性、晶圆厂或封装厂的产量,并最终影响产量。

有效的制造测试需要维护所有测试单元组件,从巨大的ATE机器到处理程序、探测器、软件、探针卡和负载板。通过反复探测和插接,支持晶圆级和封装级测试的测试板会出现错位和污染。污垢会增加接触电阻 (CRES),从而对重新测试率、产量和设备正常运行时间产生不利影响。

定期清洁探针和插座对于测试工厂来说是绝对必要的。但是这些清洁过程会影响负载板/探针卡的使用寿命。因此,测试设备公司一直在寻找最佳清洁率,利用分析来管理清洁频率。

在产品生命周期中,其他工程团队通常看不到清洁的影响。“对探针和插座测试最不了解的是清洁探针尖端和探针材料的频率和功效,例如导电与非导电、粘性与磨料或激光清洁,”全球副总裁乔治哈里斯说Amkor Technology 的测试服务。

了解清洁需求的起点是了解 CRES 及其对测试过程的影响。

CRES 基础知识

在测试环境中,关键考虑因素之一是被测设备的信号和电源焊盘/引脚到 ATE 之间的欧姆路径,以提供必要的电压和电流。该路径具有预期的阻力范围。电阻越低越好。

DUT 的电源会影响所有应用的测试。对于大型、复杂的 SoC,产品工程师更关心 CRES 对功率传输的影响,而不是信号完整性。对于专用于供电的焊盘/引脚,通常约为 40%。随着反复插入,污垢会积聚并且 CRES 上升。

在晶圆测试中管理接触电阻一直是一个挑战。它只需要足够的力来破坏金属氧化物而不会造成产品损坏。

“对于工程方面,最大的挑战是了解如何控制探针的接触电阻——以这样一种方式与芯片接触,以获得非常低的接触电阻,但基本上不会因过度驱动而损坏焊盘太多或擦洗太多,”Integrated Technology Corp. 总裁 Mark McLaren 说。“焊盘损坏的整个问题,无论是在焊盘的表面还是在下面的有源电路上,都可能是最大的问题。”

每次接触到芯片时,探针尖端都会收集更多的污垢,从而增加 CRES。而当CRES超过限制时,会影响芯片测试测量精度。每次接触都会对焊盘/凸块造成更大的损坏,这会影响引线键合和倒装芯片封装的组装过程。

当观察到较差的 CRES 时,操作员可能会增加一点超程以满足 CRES 期望并执行晶片的重新测试。这种超行程的增加,同时使更好的电接触最有可能导致擦洗痕迹特性的变化。类似地,对于封装芯片的测试,操作员可以控制施加在插座内弹簧针上的力,以实现金属间接触,从而实现良好的电传输。

图 1:探测后的 CU 柱。资料来源:FormFactor

“您如何保持稳定接触与最小化测试焊盘/凸点损坏之间的平衡?FormFactor探针业务部产品营销总监 Alan Liao 说:“当前的生产测试需要最高 100K 接触点的最高测试效率,这意味着测试过程中会发生超过 300 公斤的力反作用。” “在这些高力情况下,会有很大的反作用力返回到探针卡上。为了避免测试焊盘/凸点损坏并保持良好的接触,您可以使用 MEMS 探针,这大大降低了探针力。这种先进的探针卡架构在 300 毫米晶圆面积上实现了出色的探针平面度控制。自 2014 年以来,这些测试挑战推动了对 MEMS 高级探针卡的需求。”

对于所有类型的封装,工程师一直关注这种力的平衡。高达 75% 的封装部件仍然使用引线键合技术,焊盘上的过度驱动会对以后的测试步骤和产品质量产生负面影响。

在2009 年一项题为“晶圆探针测试的参数建模”的引线键合封装研究中,飞兆半导体的工程师使用有限元分析来理解以下参数对用于引线键合封装的芯片的晶圆探针测试的影响:探针超程 (OT)距离、擦洗、接触摩擦系数、探头尖端形状和直径。他们特别关注对焊盘下方的层间介电层的影响。引起局部拉伸应力会导致 ILD 故障,这将导致芯片级或封装级测试失败,从而导致客户退货。

在测试工厂中,平衡游戏是将 CRES 保持在确定的限制下以保持测试质量。超过该限制,产量会降低,而重新测试率会增加,从而导致 OEE 降低。

清洁选项

摩擦物理会导致磨损。在机械零件中,这会通过粘性流体减少金属与金属之间的摩擦来减少。测试工程师没有这个选项。每次插入晶圆探测器或单元处理系统时,都会发生金属对金属的摩擦。摩擦会带来碎屑、探针尖端、弹簧针和插座的磨损,从而导致更大的 CRES 值。

“每次接触垫子时,都有可能产生颗粒。擦洗垫的目的是穿透氧化铝层以接触铝垫。这个过程自然会产生铝氧化物颗粒,特别是当你在高温下测试时,它会产生更多的颗粒。” 廖说。“当你转向 C4 凸点或 Cu Pillar 焊点时,材料的熔点通常低于铝和铜焊盘。它们可以融化到您的探针尖端,这有助于提高接触稳定性,即 CRES。”

用于单元级测试的负载板上的测试插座中也会发生污染。

“插座中的引脚或探针接触到 DUT 的引脚或焊球,”Cohu 高性能接触器总监兼总经理 Dan Campion 说。“它会深入并穿透氧化物,因此它会在上面留下一些材料。现在,许多探头的设计目的是尽可能少地脱落这种材料。但随着时间的推移,它会积累起来,你需要使用一些清洁方法。”

业界已通过在晶圆和单元测试中采用清洁工艺做出回应。通过去除污染物,探头尖端或插座接口的 CRES 返回其起点。

实际使用的清洁技术因晶圆探针技术、接触器技术和处理设备而异。对于插座来说,清洗的方式多种多样,包括刷插座、压缩空气吹扫、激光清洗、使用清洗基板等。

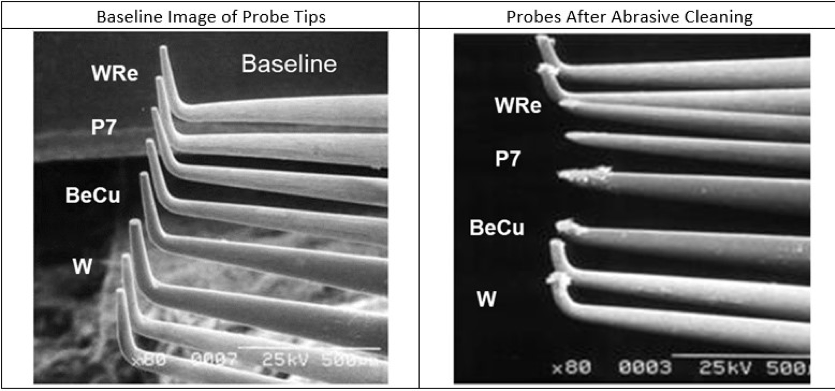

International Test Solutions 技术高级副总裁 Jerry Broz 说:“在晶圆分类期间清洁探针卡的探针时,用户可能会使用通常是研磨膜的清洁材料。” “对于不太先进的悬臂或垂直探针卡,当执行这种类型的研磨清洁时,它会去除探针材料。这种研磨清洁会产生更大的探针尖端,从而在被测设备上留下更大的擦洗痕迹。由于研磨清洁过程会去除探针材料,因此还会减少探针尖端长度并影响探针卡的使用寿命。”

图 2:清洁对悬臂探头尖端的影响。资料来源:SWTest 会议,2007

随着基于 MEMS 的探针技术的引入,该行业开发了高度工程化的清洁材料。“加载的聚合物清洁材料充当碎屑收集器,但也可以提供抛光作用,以去除探针尖端上的粘附污染物,”布罗兹解释说。“这种类型的高级清洁对于保持接触区域纹理和保持探针尖端的整体形状是有效的,以最大限度地增加探针卡的触地次数。”

清洁需要时间,并且会影响设备的正常运行时间。在手动清洁过程中,技术人员分解测试单元以移除探针卡或负载板以进行手动清洁过程。这对设备正常运行时间有重大影响。今天,所有探针都支持使用某种清洁基板对探针尖端进行原位清洁。事实上,晶圆探针卡的自动清洁只是假设。

插座自动清洁的采用率一直在上升。工程师首先必须证明它可以做到。“在 2004 年,我们实际上引入了在处理程序中实施套接字清洁的概念。当时,处理程序没有配置为适应清洁执行,”布罗兹说。

封装类型决定了 DUT 和负载板插座之间的机械接口。这反过来又决定了清洁选项。考虑夹在带引脚封装的引脚上与使用插座中的探针接触焊球之间的区别。

对插座自动清洁的兴趣与球栅阵列封装的增长相对应。焊球在触点中产生的污垢比引脚多。

“在焊球上会形成氧化物,为了保持良好的接触,你需要刺穿焊球,”坎皮恩说。“在这样做的过程中,它不可避免地会留下残留物,而如果您将引脚滑入插座的插座中,则几乎不会产生残留物。”

由于测试单元配置的不同,封装测试的原位清洁与晶圆探针测试略有不同。

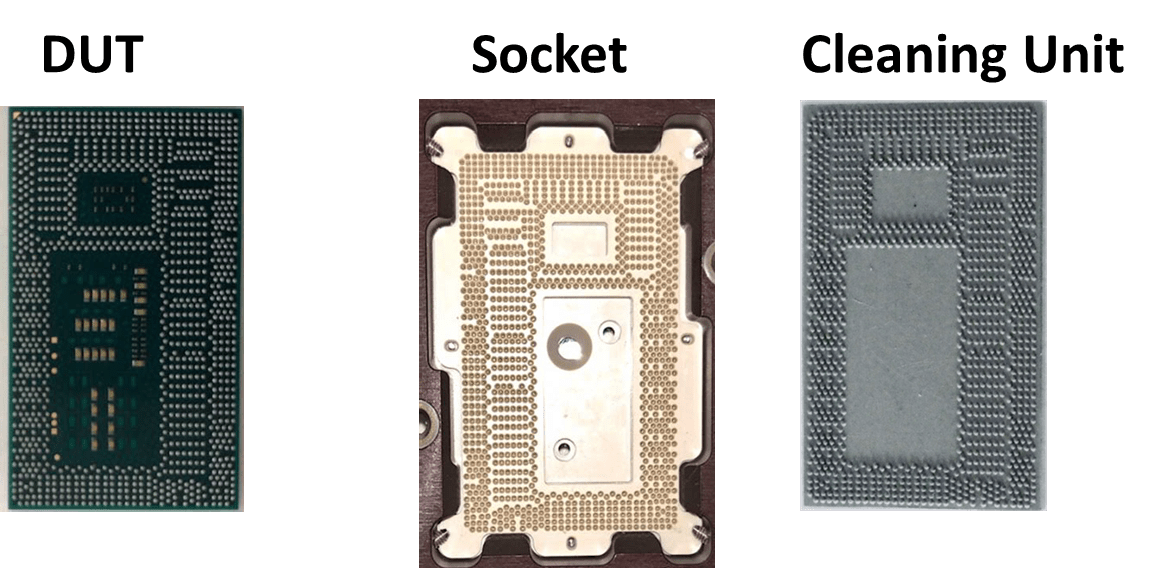

“你有一盘这些清洁设备(CD),坎皮恩说。“清洁材料是一种 DUT 替代品,与 DUT 插座接口的几何形状相匹配。您将该托盘装入处理程序。当需要清洁周期时,CD 会自动通过处理程序循环到负载板,就像被测设备一样。它们被插入插座一定次数,然后测试单元返回到生产测试。”

图 3:用于自动包装清洁的组件。资料来源:International Test Solutions,CMC 材料公司

清洁频率 清洁频率

直接影响测试接口的 CRES 以及探针和插座的使用寿命。虽然接触器和探针卡制造商提供了清洁频率的指导,但它始终需要针对被测试的特定产品进行定制。来自测试人员和测试设备的数据,结合数据分析平台,使工程师和技术人员能够进行更具响应性的定制。

清洁对于晶圆和单元级测试的成功至关重要,找到最佳清洁频率有利于探针尖端、插座寿命、重新测试率和设备效率。简而言之,这归结为您清洁的频率。

“在测试仪上,探针卡触地 50 到 100 次后,他们将拉入清洁晶片以去除附着在探针尖端的任何颗粒,”廖说。“然而,采用这种抛光工艺也会削掉探头尖端材料并缩短探头的使用寿命。探针卡供应商和测试工程师需要共同努力,以实现对 CRES 来说足够好的均衡清洁配方,同时又不会对探针卡的使用寿命产生太大影响。”

这需要某种平衡行为。Advantest America的技术和战略副总裁 Keith Schaub 表示:“如果工厂可以在 OEE 中挤出 0.5%,这实际上很重要,因为它会随着时间的推移而增加。” “更大的影响在于测试硬件寿命。你不想太频繁地清洁,因为每次你去触摸某物时,都是磨损。如果清洁太晚,则会影响产量和产品质量。”

在最终测试中,清洁策略取决于测试设施。“保守的策略是预防性维护,”坎皮恩说。“经过如此多的循环后,您会自动清洁,例如 10,000 次,或者您可能会在批次之间进行清洁。另一种方法是监控特定的测试参数——当接触故障超过一定百分比时,您将进行清洁。这更具适应性,即及时完成清洁。”

但是,他指出,盲目响应测试参数可能是一个问题。因此工厂还需要监控清洁频率,因为它可以作为更深层次需求的指标,例如更换插座、套件或检查整个机械堆栈的对齐情况。

使用数据分析平台,产品和测试工程师可以了解驱动重新测试和触发清洁周期的参数是否特定于多站点测试板。

Onto Innovation技术客户经理 Darren James 表示:“为了跟踪芯片良率和连续故障,如果单个测试站点的良率下降,可能会导致前往维修店。”

随着大批量生产——每月数百万个零件——已经对机器学习算法进行了调查,以触发清洁周期。

“我应该什么时候打扫?例如,如果接触电阻太高,他们就会使用规则,或者他们会计算出触地得分的次数,”Advantest 的 Schaub 说。“我们一直在努力提高效率和运营。您可能倾向于过早清洁,因为您不想做得太晚。这有点像转动汽车上的轮胎。您每 20,000 英里旋转一次,但这实际上取决于您的驾驶情况。如果您一直在直线行驶,那么您可能不需要这样做。您可能会行驶 30,000 或 40,000 英里。如果您在城市或弯曲的道路上开车,并且磨损严重,则您可能需要提前这样做。这就是机器学习的重点。机器学习会获取这些数据并为您计算出来,优化何时应该再次进行清理。”

结论

从一开始就需要清洁插座和探头,因为接触电阻对测试单元和芯片有不利影响。清洁是必不可少的,但与中断测试过程的所有步骤一样,仍有改进的余地。

预防性维护方法通常会导致清洁配方过于激进。一些测试设施采用了响应式方法,使用测试数据来规定清洁频率。触发器是基于统计区间限制还是基于机器学习的算法并不重要。Goldilocks 的目标是达到恰到好处的清洁量。

进行最终接触的测试硬件将经历退化。随着半导体工艺生成和封装技术的每一次进步,对此的担忧仍在继续。该行业已通过清洁技术的转变和最著名的做法做出回应,以维护对最后一厘米的测试接触至关重要的测试硬件。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学