芯片设计

作者:admin 来源:本站 发布时间:2021-10-26 访问量:2800

芯片设计是设计芯片的过程,是电子工程的重要组成部分。芯片设计的这个过程涉及到电路设计的知识及其逻辑构成。所有芯片均使用称为晶体管的基本元件制成。该金属氧化物硅场效应晶体管(MOSFET)是其用于制备复杂的电路数字芯片的基本构建块。

芯片设计的历史与晶体管的发展有关。Jack Kilby 在 1958 年开发了第一个集成电路,它只包含一个晶体管。第一IC的尺寸约为17.76 mm 2。第一个集成电路使用锗作为半导体材料。虽然锗具有很高的电子迁移率,但它仍然几乎从 IC 工业中消失,但硅仍然存在,因为它是世界上最丰富的元素。

最初,该芯片用于军事目的,但很快引起了家庭和医疗保健行业的注意。1965 年,戈登摩尔提出了一个规则,他说给定面积的芯片中的晶体管数量每 18 到 24 个月就会增加一倍。这条定律直到 90 年代末都完好无损,但随着最近尺寸缩小的晶体管的发展,这条定律不再有效。芯片中的晶体管数量已达到数十亿个。

芯片设计趋势

芯片设计的现代趋势以及先进的 EDA 工具使芯片设计比以往任何时候都更具可扩展性和可靠性。

在过去的十年中,晶体管的物理尺寸已大大减小。这导致了非常大的芯片和低电压芯片设计,这意味着芯片消耗的功率非常少,甚至只有几微瓦的功率。这使得芯片在各个市场和行业在芯片尺寸和市场渗透方面都具有高度的可扩展性。

芯片设计的另一个重要趋势是使用协同仿真(硬件和软件)设计。这样,整个算法分为两个子块:(i)需要密集计算的子模块被带到硬件即芯片,(ii)依赖于数据并参与决策的复杂模块在软件上进行处理。下面的例子是一个很好的例子,展示了如何将设计过程划分为不同的子集。

最后,IP核对于芯片设计过程非常重要。如果设计人员必须在任何时候实施复杂的设计,他都可以使用 IP 核来节省时间并降低开发风险。

芯片设计流程

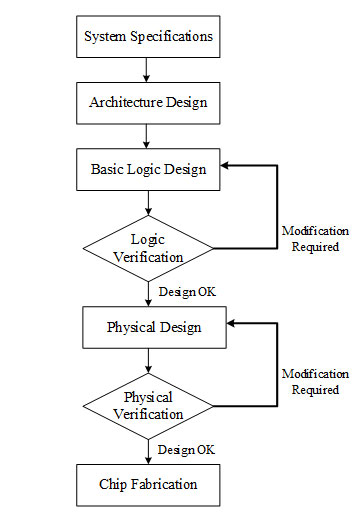

芯片设计流程与FPGA设计流程非常相似。只有一个区别:芯片是在设计完成后制造或制造的。芯片设计流程如下图所示。

出于实际原因,我们将在本文中使用 4×4 阵列乘法器设计的示例,该设计是一种数字设计。

系统规格

芯片设计过程的第一步也是最重要的一步是定义和创建系统规范。该系统的主要目的是获得相乘的 2 个 4 位输入。并且预期的结果应该是大约 8 位宽。

架构设计

下一步是设计系统的架构,我们决定将使用哪些块以及该系统将运行的层次结构。

基本逻辑设计

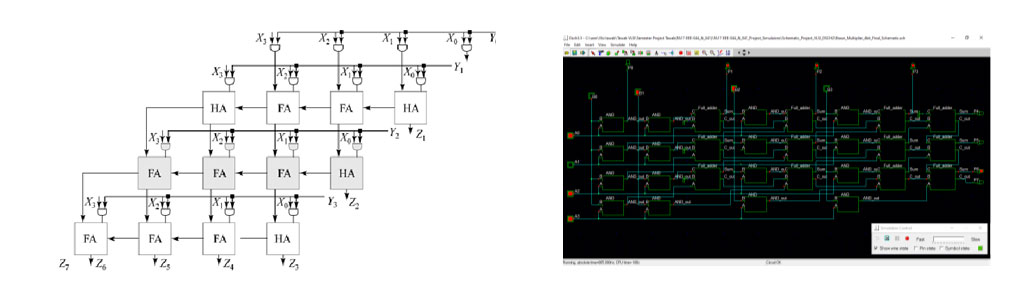

架构设计完成后,设计基本逻辑系统。对于上面引用的示例,逻辑图显示在左侧,而原理图设计显示在右侧。该原理图是使用称为 DSCH 的软件工具设计的。

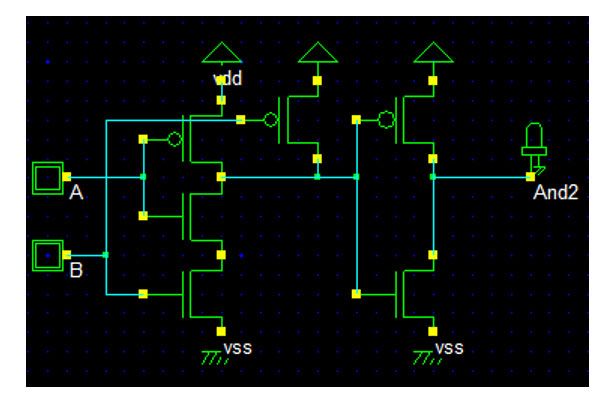

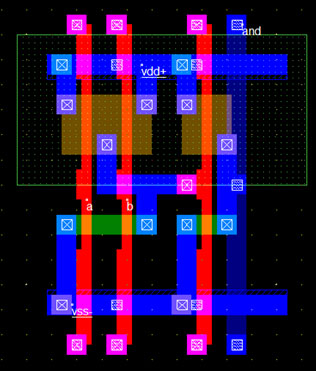

用于制作该乘法器的所有模块(AND、Half Adder、Full Adder)均由基本晶体管制成。与门的示例示意图如下所示。我们可以看到在这个简单的图中使用了 6 个晶体管,并且还有很多互连。

逻辑验证

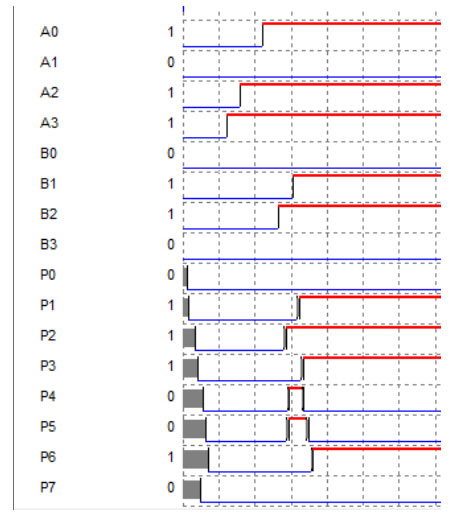

系统原理图设计完成后,下一步就是验证系统功能。这可以使用同一工具中的模拟来完成。这一步很重要,因为它有助于在初始级别进行验证,如果在系统功能中发现任何问题,可以在开始时将其删除。如果发现任何问题,则必须返回原理图设计级别并调试问题并提出更新的原理图。显示了上述系统的验证波形。另请注意,在复杂系统中,系统的模拟和验证将是一项更艰巨的工作。

物理设计布局

下一个也是最重要的步骤是将系统转换为物理级别。在此级别,原理图使用基本构建块转换为物理布局。例如,下图显示了上面显示的两个输入与门的布局。我们可以观察到每个晶体管都被相应的物理布局替换,而互连则被替换为不同的金属层,如金属 1、金属 2 和多晶硅。这似乎是一个有点复杂的过程,因为设计师必须手工制作所有晶体管和互连。

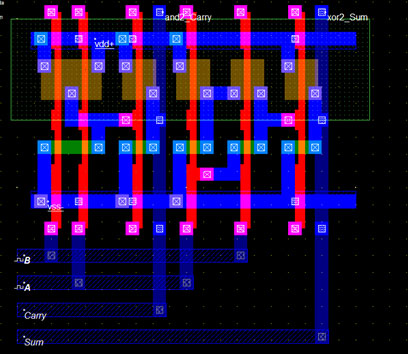

下图显示了半加器的物理布局,在这里可以观察到,随着模块链接在一起,过程变得更加艰难。因为我们必须确保所有的晶体管都正确放置,晶体管不能占用不必要的空间,所有的互连都是按照原理图设计的,多层互连是为了避免复杂性,所有需要的触点都被添加到将两个不同的层连接起来。

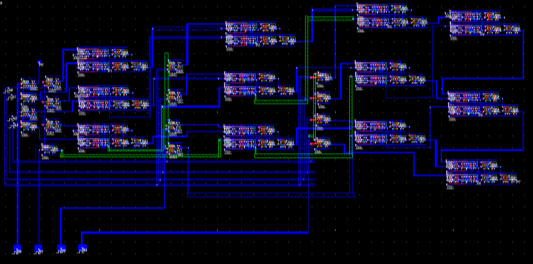

4 位乘法器的整体系统如下图所示。可以观察到,随着系统抽象性的减少,系统变得更加复杂。

物理设计验证

在进入制造工厂之前,需要对物理布局进行验证。为此使用了多种验证技术,包括 (i) 设计规则检查 (DRC),其中设计工具检查设计规则中的任何违规行为,例如金属间距、触点尺寸等,(ii) 使用布局与原理图 (LVS) 检查验证设计的布局是否与原理图设计相似,并检查所有连接并验证它们,以及 (iii) 时序和功耗分析用于验证所做的布局是否违反任何时序问题并增加不必要的延迟,如果有如有任何违规,可在需要时通过添加反相器和缓冲器来消除。时序延迟规划不当会导致操作频率降低,因此时序延迟的这种验证和校正对任何设计人员都很重要。

制造和最终测试

最后一步是物理布局设计的制作。在工具上设计系统时,所有库和层信息都由将要制造芯片的代工厂提供。在系统设计和验证之后,.GDS 文件被发送到代工厂进行制造。

最终的测试是在硬件上完成的,因为可以制作一个原型PCB,并在其上安装芯片,并将所有必要的接口添加到PCB上进行测试。对于最终测试,另一个重要步骤是在系统内添加内部测试节点,这对于在实际 PCB 上测试时调试系统至关重要。

芯片设计工具

有不同的公司提供芯片设计工具。对于设计过程的每个阶段,工具都是不同的。以下是芯片设计工具市场的两个主要参与者。

西门子为 IC 设计提供各种设计和验证工具,其中包括:(i) 信号完整性分析,以确保减少设计时间并使设计完美无缺,(ii) “Calibre Design Solutions”,用于克服电路中的电容问题和 (iii) “定制 IC”以获得完整的 . 有关该软件的更多详细信息,请访问 ( https://eda.sw.siemens.com/en-US/ic/products/ )。

Cadence是IC设计行业的巨头之一。它们提供可用于创建模拟和数字 IC 的工具。Cadence 还提供了非常有效的工具,通过提供自动布局生成工具来减轻设计师的设计负担。通过这种方式,设计人员以 RTL 语言创建顶级模块,工具将其转换为物理级别。Cadence 工具的链接是https://www.cadence.com/en_US/home/tools/custom-ic-analog-rf-design/circuit-design.html。

芯片设计的未来

改变芯片设计行业未来的两个因素是:(i) 个位数节点的引入 (ii) 设计工具的进步。第一个是10nm以下的硅片,它为数据中心带来了CPU和加速器等新型高计算芯片,这将使我们拥有数以百万计的计算能力。因此,第二个因素支持这种发展。现代工具使设计人员能够克服物理设计过程中的繁琐工作,并为他们提供使用自动设计工具创建芯片的方法,其中设计人员在更高层次上工作,而工具将更高层次的系统转换为物理层次制造设计。这意味着更快的芯片设计周期。

上一篇:芯片设计的变革

下一篇:RISC-V 是未来吗?

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学