芯片设计的变革

作者:admin 来源:本站 发布时间:2021-10-26 访问量:2360

设计芯片的指南正在消失或变得不那么重要。虽然今天的工程师有更多的选择来定制设计,但他们对什么最适合特定应用或这些努力的投资回报几乎没有方向。

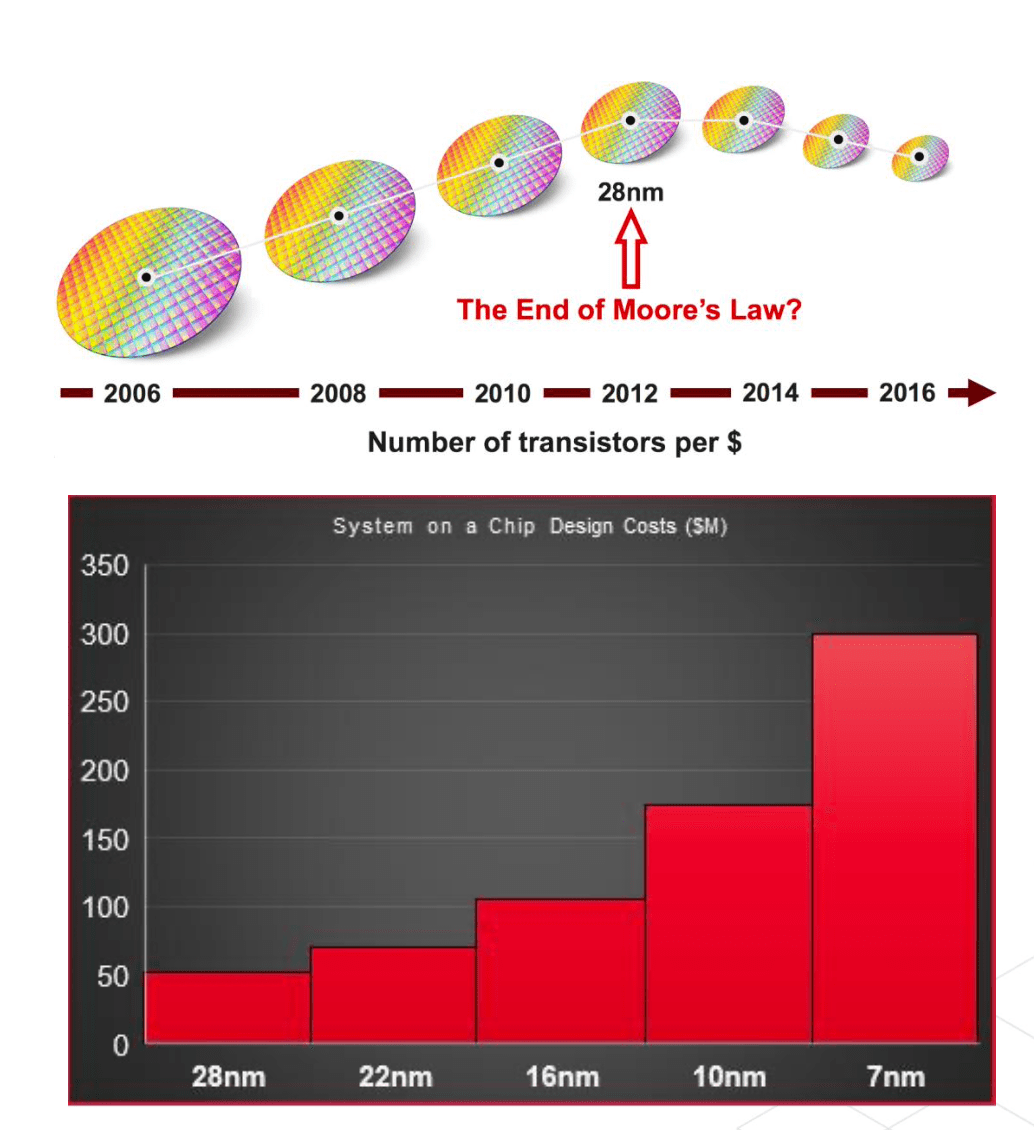

对于芯片架构师来说,这被证明是一种财富的尴尬。然而,这种设计自由伴随着巨大的财务风险和对更长芯片寿命的更高责任。直到并包括 28nm 节点,这些类型的决策由 ITRS 路线图和摩尔定律定义。但是随着缩放的功率和性能优势开始减弱,以及设计和制造 3D 晶体管的成本开始呈上升趋势,半导体经济学开始变得截然不同。

芯片制造商现在可以利用各种异构选项,创建更多定制设计以适应特定数据类型或最终应用。这一点在大型数据中心(谷歌、亚马逊、阿里巴巴和 Facebook 等巨头一直在设计自己的芯片)以及汽车等市场(特斯拉和大众等原始设备制造商正在竞相开发越来越多的自动驾驶汽车架构)中表现得尤为明显。使用内部设计的硅。但是所需的资源和失败的风险也在增加。

所有这些因素对芯片行业以及使用这些设计的系统公司都有广泛的影响。其中:

新工艺节点的推出正在加速,而不是放缓,但每个新节点的优势在 20nm 之后缩减至不到 20% 的功率/性能改进。因此,设计团队正在将系统级封装和/或片上系统用于越来越多的异构设计,IP 在不同的工艺节点上开发。这使得集成变得更加困难,并且可能在不同组件之间产生老化差异,并且更难以预测它们在该领域随时间推移的表现。

正在定制设计以应对终端市场以及新兴市场的快速变化,这使得实现规模经济变得更加困难。这些经济性基于单一设计制造的芯片数量以及多代衍生芯片。甚至 IP 也在被定制,这带来了涉及时序、验证、可制造性和良率的挑战。

终端市场正在努力寻找利用半导体技术的最佳方式,其中一些相对较新。例如,汽车原始设备制造商在过去五年中在寻找最佳方法时已多次更改架构。除此之外,各种技术正在推动新市场和现有市场的融合,这些市场通常来自以前不相关的业务部门。过去,通常是相邻的市场合并在一起。今天和将来,这些邻接可能更难识别,例如用于建筑物中备用电池的汽车。

简而言之,芯片行业正在以新的方式分解和重新聚合。虽然这为芯片制造商提供了巨大的设计自由,但它也以不明显的方式改变了业务和技术关系。与此同时,这些变化正在颠覆过去几十年几乎可以直线绘制的一系列假设,当时的主要目标是更小、更快、更低功耗和更便宜。更令人困惑的是,地缘政治压力在中国形成了一个独立的供应链,选择和未知的数量正在显着增加。

“这与我们能否制造越来越小的晶体管无关,” Arm首席执行官西蒙·塞加斯 (Simon Segars) 说。“我们在边缘人工智能、需要利用一组技术的微型传感器方面同时出现了爆炸式增长。我们在云中进行了大量计算,您需要担心其效率。我们有新的网络技术不断发展,需要新的无线和射频技术。它同时向多个方向行驶,这使得使用路标变得困难。”

结果是存在一定程度的不确定性和创造力,这是计算早期以来从未见过的。

英特尔高级副总裁兼技术开发总经理 Ann Kelleher 说:“您正在努力在给定时间为客户提供最好的产品。” “但是菜单上有更多选项,而且它更像是点菜菜单而不是固定菜单。过去,一切都基于您正在使用的节点。我回到设计支持团队,以及流程和包装之间的设计工作,关于我们如何为未来的给定产品获得最佳答案,有很多积极的讨论和辩论。”

Kelleher 指出,这包括许多因素,例如工艺、包装内的不同瓷砖选项、成本和其他特定于市场的因素。“有很多方法可以到达那里,供应链本身变得更加复杂,”她说。“根据特定产品及其特定功能,我们将讨论如何使用最可制造的瓷砖版本以及供应链来实现这一目标。”

选项数量激增,但如何最好地利用这些选项的指南正在消失。“在过去的 10 年里,你曾经可以说,'我的软件正在改变,所以我可以使用下一代处理器,'” Imperas 的首席执行官 Simon Davidmann 说。“今天的问题是没有适用于所有这些不同软件问题的下一代标准处理器。”

现在需要更多资源——工具、人力、金钱和时间——来开发领先的芯片。在电源方面,挑战包括向晶体管提供足够的电流,以及在晶体管充分利用时冷却这些晶体管。关于应该如何对内存和逻辑进行分区,以及应该由谁进行分区,存在一些问题。有更多潜在的相互作用和物理效应,例如功率、电磁干扰和基板噪声,以及在最先进的节点上需要应对得越来越多的量子效应。不仅在晶圆厂,而且在现场和随着时间的推移,确保一切都得到充分验证和测试是一项挑战。

由谁设计,为了什么?

所有这些都会对设计、芯片或 IP 模块根据规范预期运行多长时间以及芯片、封装和系统的价格标签产生重大影响。过去,这是由 OEM 定义的,芯片制造商会根据有限数量的选项(例如工艺节点、功率预算和成本)为规范构建芯片。那些通常定义的性能、功率和面积 ( PPA )。

今天,这种缓冲已经基本消失了。芯片制造商直接与系统公司合作制造芯片,或者系统公司自己做。最初的规划涉及一个多学科的工程团队,可能还有一个或多个 IP 供应商、EDA 公司,以及大型系统公司和 IDM(如 Apple 代工厂)。

对 PPA 方程的任何部分的关注可能因一个应用程序到另一个应用程序而有很大差异。例如,在超大规模数据中心的环境中设计芯片或模块的成本可能远不如节能设计的节省重要,这可以被服务器的供电和冷却机架的高成本所抵消,以及性能更好的系统可以在给定的足迹内为更多的客户提供服务。它还可以通过更好的监控技术来确定何时需要更换芯片,而不是每四到七年批量更换设备以避免停机。

“这是关于真正了解最终用户应用程序是什么,”西门子 IC EDA执行副总裁 Joseph Sawicki 说。“该最终用户应用程序可能不仅仅是简单的数据处理。它可能涉及与外部世界的接口,并且它正在改变设计和验证,因此它必须跨越并越来越多地处理验证在现实世界中运行的最终用户软件堆栈的那些方面,这是更多的数据处理方式设计方面,在最终用户体验上投入更多,以及更全面地了解如何优化设计。”

另一方面,如果它是汽车内的传感器融合模块,设计成本是一个压倒一切的问题。但即便如此,模块在其预期使用寿命内与车辆中的其他组件完美配合的能力也可能不那么重要。

Synopsys产品管理和营销集团总监 Hany Elhak 表示:“如果我们考虑过去的规模缩小,总是会转向具有更小的晶体管和更大 SoC 的更低工艺节点。” “现在,缩放正在成为采用不同技术设计并针对不同应用定制的不同芯片,它都是更大系统的一部分。缩放现在以不同的方式表现出来。所以这不仅仅是摩尔定律。这是一个系统的系统。”

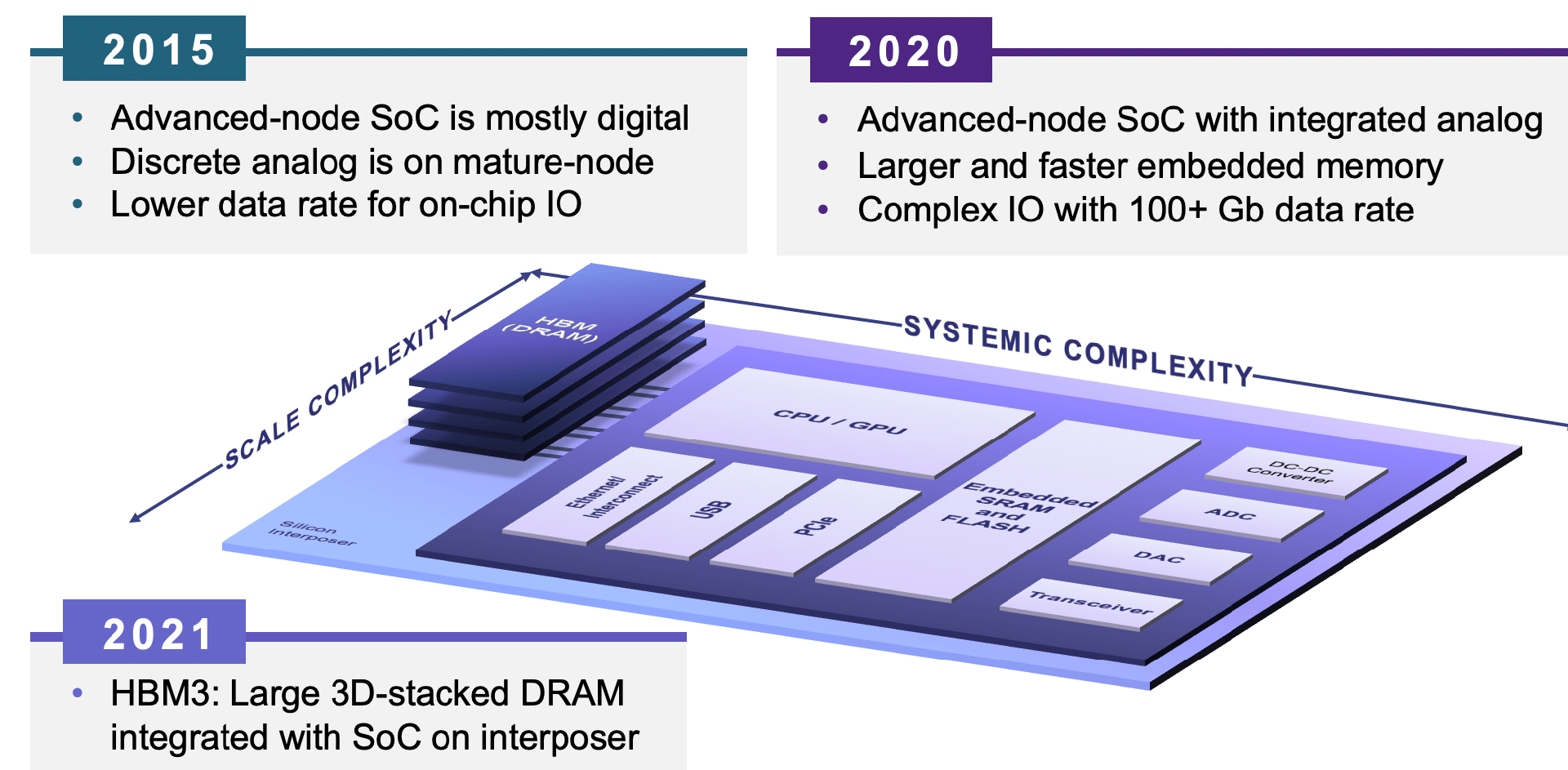

图 1:IC 设计超融合。资料来源:新思科技

这些系统的系统也可以改变。在更好的连接性和使用机器学习来提高盈利能力的推动下,一些最深刻的技术变革正在传统的低技术行业内部发生。

“不同技术的融合正在发生,而且还会继续发生,” Aldec营销总监 Louie De Luna 说。“有 5G、人工智能、机器学习。你甚至可以在国内市场看到这一点。有了智能电视,您现在可以在 YouTube 上进行搜索。”

以前截然不同的市场之间的界限要么已经模糊,要么开始模糊,半导体设计将跟随或推动这些变化。“我们与航空电子设备客户的很多对话都围绕 FPGA,”De Luna 说。“FPGA 可用于控制引擎、电子设备、起飞、导航等等。我们现在看到的是越来越多地使用高速接口,如 PCIe 和以太网。但是当我们使用这些高速接口时,处理 DO-254 是非常困难的。您需要捕获串行高速接口的结果,而没有办法做到这一点。当你调试它并查看波形时,有很多确定性的结果,所以很难调试。”

芯片行业及其所服务的市场内的变化率不断变化,使得开发标准化 IP 和芯片变得更加困难。大型 IP 公司已经看到这种趋势一段时间了,因为它们的最大客户一直要求对商业 IP 进行调整。

所有这些活动的影响使另一个行业指南成为焦点,Makimoto's Wave假设定制设计和标准产品之间有 10 年的周期。虽然基本想法仍然合理,但由于非常不同的经济学以及全新的应用程序,从高峰到低谷的时间框架正在延长。

Cornami 总裁兼首席执行官 Walden Rhines 说:“Makimoto 正在谈论一个更短的波浪。” “今天,它看起来更像是 30 或 40 年。这是我最后一次记得如此大规模的事情是在 1980 年代微型计算机行业建立了自己的晶圆厂。”

这不再像用标准化部件替换定制部件那么简单,它引发了关于衍生芯片在该方案中的工作情况的问题。当 AI/ML 被添加到设计过程中时,这种转变变得尤为明显。

Cadence数字和签核营销高级组总监 Kam Kittrell 说:“过去,我们进行了重播,然后重用了模型。” “今天,很难判断一个模型是否可以重复使用。如果您采用相同的库,例如 GPU 的着色器核心,现在您将获得不同的工作电压,因此您之前进行的训练甚至与此无关。”

图 2:晶体管成本上升。资料来源:节奏

老化增加了另一个变量。老化可能会有所不同,具体取决于导线的尺寸(RC 延迟)、电介质的厚度以及芯片各个部分在其整个生命周期中的使用强度。电路的低利用率,即使在高级节点,也可以显着增加其预期寿命,而在更老的节点上开发的电路的更多使用会缩短其寿命。

Kittrell 说:“过去,人们通过一种特殊的方法预测了衰老。” “就像,'我认为它会老化这么多。' 汽车客户之所以使用它,是因为他们对可靠性有要求。一个电路必须工作 20 年。现在,超大规模人员担心老化,因为高级节点上的高活动率可能会在一年内造成相当显着的性能损失。他们必须确保如果它在 4 GHz 下运行,它将保持在 4 GHz 范围内,并且他们通过稳健的优化来做到这一点。”

RISC-V的引入和越来越多的采用增加了另一个变量。开源模型不是专门使用商业内核,而是允许用户自定义指令集架构源代码,只要它可以通过 RISC-V 国际认证。RISC-V 允许软件和硬件之间更紧密地集成,特别是针对特定用例或应用程序必不可少的功能。它还为芯片设计团队带来了一系列新挑战,以及改变 PPA 方程式的潜力。例如,定制的 RISC-V 加速器可以与现成的处理器一起打包,以比设计整个模块更快、更便宜地创建特定领域的设备。

“你可以使用 RISC-V 通过在指令集扩展方面添加一些新的东西来处理信号处理或成像处理,而 RISC-V [International] 实际上鼓励你这样做,因为它已经告诉你如何进行定制, ” Codasip 的CTO Zdenek Prikryl 说。“但如果你设计一个加速器并将其放入一个更大的系统中,你可能会拥有数十或数百个不同的加速器。你必须确保一切正常。你必须在验证中投入很多。”

更智能的工具和更智能的工具使用

技术的快速发展,加上对特定领域解决方案的广泛需求,为 EDA 行业创造了潜在的财富。过去两年的收入一直稳定在两位数,最近它创造了一些收入增长记录。

但是新设计中涉及的变量太多,EDA 公司正争先恐后地跟上步伐。在某些情况下,需要为每个新项目修改工具。

“在硬件领域,非常聪明的人提出了解决问题的新架构和新想法,他们用疯狂的想法扩展设计工具,让我们重新思考我们如何做事和做什么,”因佩拉斯的大卫曼说。“我们需要每年重新调整我们的模拟器,以使其做得更好。有人向我们提出了一个新问题,我们会说,‘好吧,我们怎么做?我们试图解决它。有时我们会成功,有时我们无法提供帮助,但是这种将设计扩展到我们所看到和正在开发的所有新电子产品中的做法是惊人的。对于电子设计领域来说,这是一个令人兴奋的机会。”

这也很困难。“我们正在努力解决两个问题,”Synopsys 的 Elhak 说。“传统的电路现在更大更复杂,以更高的频率运行,并且它们具有更多的寄生效应。这就是规模问题,我们正试图通过提供更快的模拟和更高容量的模拟来解决它。这是已知的问题。我们正在努力解决的另一个问题是,现在我有许多不同类型的电路,它们是这个更大系统的一部分,它们需要一起设计。我们需要为这些不同的设计团队制定一些共同的流程,这样当他们尝试将这些东西连接在一起时,我们就不会在设计周期结束时遇到问题。他们需要从一开始就一起工作。”

在这方面,标准非常有帮助。虽然芯片本身的标准化程度越来越低,但各种流程和工具的数据格式却在朝着相反的方向发展。这有助于 IP 表征以及不同芯片和系统之间的互连。

“这是重点之一,”弗劳恩霍夫 IIS设计方法学部门负责人 Roland Jancke 说。自适应系统工程部。“您需要标准化数据格式,以便您能够在模拟器之间交换信息,并且您需要一个通用接口来分析数据格式。我们目前正在与合作伙伴合作实现任务配置文件格式的标准化。因为价值链中有不同的层次和不同的供应商,所以你必须看看你是为什么设计系统或用什么来测试它的。您用来设计系统、测试系统和验证系统的任务配置文件是什么?该系统级用于电路级开发的不同向量有哪些,等等?使用测试设备的公司提出了一些问题,即我们是否可以以某种方式标准化任务配置文件格式,以便能够描述这些测试向量,

学习曲线

虽然所有这些看起来都有些混乱,但有一个重要的常数——学习曲线。在过去近七年中绘制时,它一直是一条直线,表明每个晶体管的成本将继续下降,但从相同的缩放角度来看则不一定。

“摩尔定律只是一个特例,您通过缩小特征尺寸和增加晶圆直径来降低所有成本,”莱因斯说。“但学习曲线看起来和以往一样可预测。如果您在 NAND 闪存封装中放置 512 层,并且与 512 封装相比,您在封装上节省了大量成本,那么每个晶体管的成本就会降低。学习曲线并不关心您如何到达那里,只要您达到每个晶体管的成本即可。如果你用封装来做,那没关系,即使它引入了其他工作,比如当你开始在逻辑上堆叠内存时的热分析,甚至内存上的内存。如果你通过缩小晶体管来做到这一点,那也没关系。”

在复杂的设计中实现同一目标的方法有很多种,而且比过去要多得多。但是,如果没有定义行业公认最佳实践的指南,挑战在于让其中至少一个按预期工作。

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学