重新思考内存芯片设计和验证

作者:admin 来源:本站 发布时间:2021-09-02 访问量:1354

半导体开发一直在变得更具挑战性,这对任何人来说都不是什么秘密。每个新的工艺技术节点都会在每个芯片中装入更多的晶体管,从而产生更多的电气问题并使散热更加困难。布局规划、逻辑综合、布局布线、时序分析、电气分析和功能验证将电子设计自动化 (EDA) 工具发挥到极致。需要数百个时钟和电源域来提供灵活性并适应来自不同来源的 IP 块。最重要的是,片上系统 (SoC) 设计将并行处理和嵌入式软件添加到组合中。

设计领先的存储芯片需要处理许多相同的问题,同时也给开发团队带来了额外的挑战。分立存储芯片通常是为每个新节点开发的最早和最大的产品类型之一。分立存储器供应商积极且不懈地追求技术扩展,以保持性能和成本领先地位。然而,摩尔定律的放缓意味着仅靠更小的几何尺寸是不足以跟上市场需求的。供应商还必须通过架构创新和越来越快的接口不断创新。

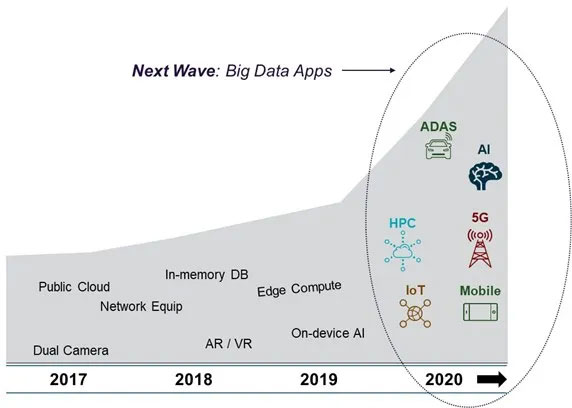

有许多苛刻的应用程序给内存供应商带来压力并推动产品需求。基于云的高性能计算 (HPC) 和大数据应用程序尽可能多地占用内存以寻求性能。人工智能 (AI),尤其是机器学习 (ML),对于以新颖而强大的方式利用这些数据至关重要。基于云的人工智能应用需要高密度、高带宽和多端口内存来整合和分析来自多个来源的数据。边缘 AI 和物联网 (IoT) 设备受益于具有高能效的较小芯片。

可能没有比现代汽车更广为人知的苛刻应用示例了。高级驾驶辅助系统 (ADAS) 和新兴的全自动驾驶汽车“美丽新世界”对 AI/ML 提出了大量要求。他们相应地需要大容量、快速的存储器,即使在困难的道路环境中也非常可靠。自然语言处理 (NLP) 是 ML 的另一个众所周知的用途,它根据许多真实世界的例子随着时间的推移调整和扩展其准确性。最后,智能手机和平板电脑,尤其是那些使用 5G 技术的智能手机和平板电脑,需要具有高性能和尽可能低功耗的存储器来延长电池寿命。

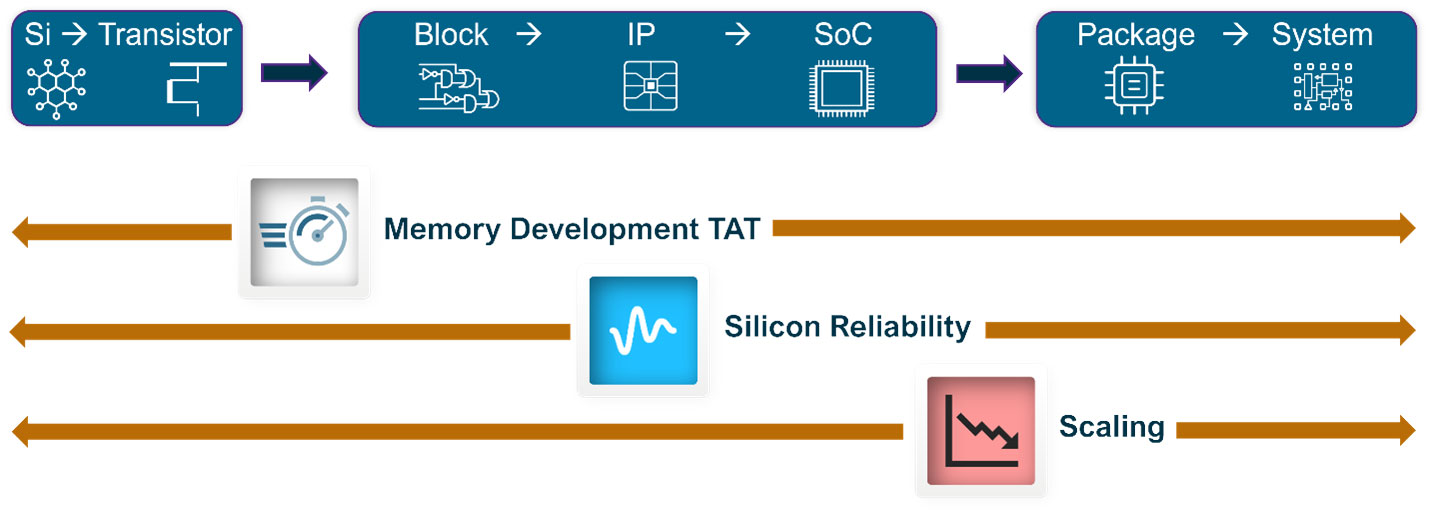

所有这些要求苛刻的应用程序及其共同的潜在因素给存储器设计人员带来了许多挑战。一些长期存在的挑战加剧,而最新的技术节点引入了额外的问题。挑战可以分为三大类。

缩放

首先是技术、性能和容量的扩展。应用和市场需求迫使设计团队在他们开发的存储芯片中不断提供更高的性能、更高的能效和更高的容量。这些要求推动了向新节点的迁移,并需要更多创新的设计技术。它们还直接转化为对 EDA 工具的要求,以处理更大、更复杂的设计。这些工具必须提供更高的容量和更快的运行时间。他们还必须支持设计人员寻求更好的功耗、性能和面积 (PPA),同时保持高质量的结果 (QoR)。

硅的可靠性

第二组挑战涉及芯片可靠性,这已成为诸如自动驾驶、航空航天和国防以及医疗等关键任务应用的一个更大的因素。满足这些应用的内存 PPA 要求所需的新节点和新颖架构会带来高度风险,如果在开发过程中处理不当,可能会影响可靠性。为了最大限度地减少创新和确定性交叉点的这种风险,设计团队必须采用先进的建模和验证技术来弥合技术到设计的差距以及设计到硅的差距,并确保硅按预期运行在开发过程中。他们必须开发并强制使用强大的流程设计工具包 (PDK) 来推动准确的设计支持。

在更广泛的范围内,存储芯片的可靠性需要全生命周期管理,从硅前设计到生产制造甚至现场部署。需要对可变性和可靠性进行分析,以确保在各种操作条件下的设计稳健性,并最大限度地减少缺陷逃逸。功能安全验证需要满足汽车市场的 ISO 26262 合规性和其他应用的相关标准。有效的良率管理必须确保能够生产出足够可靠的硅,同时仍满足成本目标。硅上监控提供整个测试过程中的数据,如果最终用户同意,可以在芯片的整个工作寿命期间对其进行监控。

内存开发周转时间

最后,鉴于需要在竞争激烈的终端市场满足各种应用需求,因此越来越重视存储器开发周转时间 (TAT)。设计团队需要在他们的整体存储器开发工作中“左移”,以满足定制芯片的市场需求。设计技术协同优化 (DTCO) 历史上并未用于存储器开发,必须采用这种方式,以便设计人员可以在“硬化”这些选择之前快速探索和协同优化新技术和设计技术。在设计阶段需要更快的验证运行时间和对电气和可靠性影响的早期认识,以加速设计验证。通过注入经过验证的、快速的、高效的数字设计和验证方法使设计团队能够进一步加速设计和验收。必须采用设计-测试和设计-封装协同优化来加速设计、测试和封装验收。

使用修补在一起的点工具集合无法满足所有这些挑战和要求。存储器设计人员需要一套全面的 EDA 解决方案集,以满足他们在整个存储器开发生命周期中的要求。现在是 EDA 供应商重新考虑当今现代和复杂存储器设计的解决方案开发的时候了。

上一篇:是什么让城市变得更“智能”?

下一篇:在 IC 制造中的YMS良率

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学