3nm芯片的巨大挑战

作者:admin 来源:本站 发布时间:2021-09-14 访问量:1238

模拟工程师在 3nm 方面面临着巨大挑战,迫使他们想出创造性的解决方案来解决每个新工艺节点的一系列问题。尽管如此,这些问题必须得到解决,因为没有至少一些模拟电路,任何数字芯片都无法工作。

随着制造技术的缩小,数字逻辑在功率、性能和面积的某些组合方面有所改进。工艺技术针对这些进行了优化。然而,模拟基本上必须接受它所得到的。随着每个工艺的缩小,电压下降,寄生数量增加,噪声和变化增加。新技术,例如全环栅、冲击灵活性和模拟工程师,通常不得不重新发明他们的工作方式,以保持相同的功能,有时以牺牲面积为代价。

至少,每个 SoC 都会有某种类型的接口或外设。“将有一个用于 PCI Express 或 USB 或任何类型通信的 SerDes,” Synopsys产品管理和营销组总监 Hany Elhak 说。“该芯片可能会与内存通信,这需要 DDR 或 HBM 之类的东西,这是另一个复杂的模拟块。所有这些大型数字 SoC 都将包含嵌入式 SRAM,这是一个模拟电路。模拟是任何 SoC 不可或缺的一部分,如果 SoC 走向 3nm,那么模拟也将走向 3nm。问题是所有这些高级节点都是为数字设计的。模拟设计师需要跳过障碍才能使事情发挥作用。”

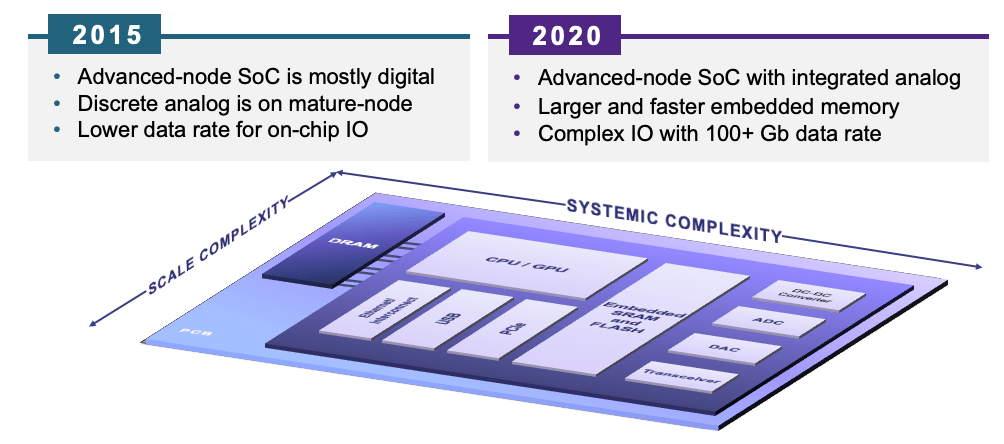

图 1:模拟在设计中的作用越来越大。资料来源:新思科技

它需要不同的思维方式。Cadence高级解决方案架构师 Jeff Johnson 表示:“虽然这是一个数字过程,但模拟设计人员正在寻找应用这些技术来构建模拟模块的方法。” “在某些情况下,他们会建立更多的校准。过程变化变得如此之大,而数字逻辑又如此廉价,以至于您可以添加校准回路或以不同的方式做事。”

这是否实用是另一回事。Synopsys 的产品营销经理 Priyank Shukla 说:“我们将在明年初在 N3 中流片我们的 PCIe 和 PHY,所以我们已经完成了这些设计。” “模拟设计师总是想出创新的电路解决方案来解决工艺问题。在模拟设计中,感兴趣的重要参数之一是电源电压,它下降到 1.4 伏,而不是 1.5 伏。我们解决了这些限制并提出了新的架构。模拟设计的另一个大问题是匹配。每个晶体管都单独运行,您必须匹配两个晶体管才能发挥其性能。”

最少的模拟构建块

对于数字,有一个简短的原始门、寄存器和存储器列表,所有设计都由这些构成。模拟有一组类似的基本块。“模拟的基本模块是诸如带隙、运算放大器、PLL、比较器、数模转换器 (DAC) 和模数转换器 (ADC) 之类的东西,”Cadence 的 Johnson 说。“如果你有这些积木,你可以用它们做很多事情。例如,A SerDes 由 PLL、带隙、比较器和 ADC 组成。”

其中一些块变得更具挑战性。“带隙电路是一个关键模块,它为整个 SoC 提供恒定电压,”Synopsys 的 Shukla 说。“在前几代,这个带隙是硅的带隙电压,为 1.2 伏。在 3nm 工艺节点,电源本身非常接近此值,因此您需要一种新设计来在您的 SoC 中创建一个恒定的参考电压。”

要提供数字电路所期望的功能,还需要许多其他模块。“电源管理需要交流/直流转换器和其他模拟电路,”Synopsys 的 Elhak 说。“与传感器接口的芯片将需要 ADC。在数字 SoC 上始终需要 PLL 来生成时钟。PLL 是当今任何 SoC 中都需要包含的非常重要的模块,即使它是纯数字的。”

但并非所有模拟功能都可以在最新节点中经济地构建。“模拟块的面积与数字块的扩展方式不同,”西门子 EDA产品管理负责人 Sathishkumar Balasubramanian 说。“例如,承受一定电流的 100 欧姆多晶硅电阻器在 28 纳米工艺中的尺寸与在 180 纳米工艺中的尺寸大致相同。或者 LC 振荡器中使用的电感器的尺寸也不会按比例缩小。”

重新架构

匹配一直是模拟的重要功能。“你会制造大、宽、长栅极长度的器件来尝试匹配,”约翰逊说。“随着流程的变化,你只需改变这些事情的工作方式,你实际上可以通过使用我们所谓的堆叠门来提出你的匹配功能来节省面积。或者我可以插入一个 ADC 来校准一些东西。它可能比尝试构建一个大到在我想要的所有角落都匹配的差分对要小得多。到我这样做的时候,它可能需要消耗多少电量,而且面积会很大,这不切实际。”

可变性带来了很多挑战。“这意味着你必须运行更多的蒙特卡罗模拟,”Elhak 说。“这也意味着设计师需要创新的架构来校准流程变化。这些可能是数字环路,甚至是增加模拟电路复杂性的软件环路。EDA 的一大创新是变异性分析,即高 Sigma 蒙特卡罗,它使用机器学习来更快地运行蒙特卡罗分析。从工具的角度来看,这些都是解决这种可变性问题的重要领域。”

获得第一个芯片

在您拥有芯片之前,必须对模型和工具建立一定程度的信任。“这一切都始于 PDK,您必须信任 PDK 和工具,”舒克拉说。“作为 SerDes 设计师,一旦拥有芯片,我就可以进行关联。这介于我的设计和我实际看到的模拟性能之间。在那之前,我相信代工厂提供的 PDK。”

这些 PDK 随着时间的推移而发展。“代工厂有非常具体的发布方式和编号方式,”约翰逊说。“即使在他们进行所谓的生产发布之后,他们也经常发现某些事情发生了变化,或者他们没有获得他们想要的产量,因此他们做出了巨大的改变,使设备性能与您开始时相比发生了显着变化。它开始是一个非常理论化的东西。然后随着他们获得更多数据,他们会收紧这些事情。”

第一个概念证明很重要。Elhak 说:“在开发 PDK 时,有一些初始工作已经完成,代工厂将一些硅片进行流片。” “它将有一些晶体管,它会有一些门和其他电路,并在此基础上改进 PDK 模型。从晶体管模型中,您可以运行 SPICE 仿真来表征数字门构建模型的延迟、噪声和泄漏,这些模型稍后用于布局和布线、时序和电源签核。但这一切都始于定义 PDK。一家工具公司和代工厂合作,并与初始硅进行晶体管级关联。我们对开发 PDK 的团队和过程充满信心。”

与过去相比,可以提前完成更多工作。“一些客户无法等待设备模型和 PDK 的验证过程,”Elhak 说。“这就是 TCAD 出现的地方。模拟团队与 TCAD 团队合作进行所谓的 TCAD 设计协同优化。标准流程从 TCAD 开始,以开发流程并定义设备模型。这用于实际构建原型,然后使用开发的设备模型来运行电路仿真。”

游戏规则改变者

随着行业向 3nm 迈进,模拟设计师必须应对的不仅仅是工艺变化。新晶体管与其他变化一起发挥作用。“下一个游戏规则改变者是环栅(GAA) 晶体管,” Fraunhofer IIS自适应系统部工程高级系统集成组组长兼高效电子部门负责人 Andy Heinig 说。“目前还不清楚是否所有代工厂都会在 3nm 开始使用它们,但如果它们来了,模拟块非常困难。所有晶体管都必须在非常规则的网格中实现,这使得很难为模拟组件获得正确的尺寸。”

GAA 确实有一线希望。“GAA 实际上有助于控制晶体管的阈值电压,”舒克拉说。“你可以更好地控制晶体管的性能。但是晶体管的长度是有限的,因为您要从四面八方覆盖晶体管。不同的宽度和长度比可以实现不同性能的晶体管。这是模拟设计师在这个工具箱中拥有的两个参数。”

并且根据技术的实施方式,其他选择也是可能的。“您现在有了一种创建并行设备的新方法,”约翰逊说。“您可以选择使用手指或在堆栈中向上移动。它将允许一些非常好的压缩,以及一些出色的晶体管性能。”

但也有缺点。“使用 GAA,电容会增加,”舒克拉说。“而且你不仅在栅极和漏极之间有电容,还有体和漏极等。这变得难以补偿。当您只有一个控制门时,就会产生寄生电容,这很容易理解。但现在有了 GAA,电容及其补偿就成了模拟的问题。”

另一个即将发生的潜在变化是埋入式电源轨. 这将电源轨移动到晶片的背面,通过晶片的通孔来传输电源。“美妙之处在于它释放了晶圆正面的金属以进行布线,”约翰逊说。“它还消除了很多寄生效应。由于线路的收缩,电阻增加了,当您有很多线路,并且必须布线电源和接地时,您最终会得到一大堆电容。这修复了很多。您可以通过使电源和接地远离高速信号来真正减少电容。如果需要,您可以使电线更宽以降低电阻,而无需付出很大的电容代价。我从中看到了很多理论上的好处,但在某些情况下,实用性才是最重要的。当你实施它时,它到底是什么样子的?”

代工厂的差异

随着这些新技术的引入,所有代工厂不太可能同时或以完全相同的方式采用每种技术。业内文献表明,对于 GAA 和埋入式电源轨,这一点将非常明显。这给 IP 开发人员带来了额外的负担,因为他们必须为每个流程定制甚至重新设计他们的模拟块。

“每个代工厂都提供不同的 PDK,并且在模拟中使事情变得更加困难,”Shukla 说。“考虑匹配,一家代工厂将有一种方法来确保两个晶体管之间的匹配,而另一家代工厂则有自己的方式。这意味着我们需要不同的技术来应对不同流程带来的这些挑战。我们提出了一些最佳实践,而且我们有作为 IP 供应商的经验,所以对我们来说更容易。但对于专注于一个代工厂的一个工艺节点的公司来说,如果他们要跨界设计,他们会发现它具有挑战性。”

这可能意味着妥协。“我们尽可能地将一切标准化,”约翰逊说。“在 28nm 中,我们采用了基于行的方法。在这种方法中,我们限制了设计师在进行设计时的选择。他们无法选择任何他们想要的门长度,他们无法选择他们想要的任何宽度。我们给了他们一张显示选择的表格。这限制了他们的选择,并使许多代工厂差异正常化。作为我们方法开发的一部分,我们会查看流程,并为我们正在做的 IP 提出我们认为正确的数字,例如 SerDes 和 DDR,然后将其标准化。我认为这与我们将要与 GAA 做的事情完全相同。

这正成为一个更重要的考虑因素。“许多客户正在采用多晶圆厂战略,因为他们无法保证一个晶圆厂的产能,”Elhak 说。“代工厂之间的技术存在差异,这意味着模拟设计师需要创建不同的设计,即使是同一个芯片,以便能够在多个晶圆厂制造。对于 IP 提供商而言,这种限制甚至更大,他们现在需要在大量工艺节点上创建相同的 IP。”

分析与验证

验证团队的规模增长速度远快于设计团队的规模。“过程变得非常复杂,寄生的数量显着增加,”约翰逊说。“如果你有 100 个节点,每个节点都可以独立变化。不仅每个节点可能不同,而且每个节点内的寄生参数也可能不同。您需要进行包含所有这些的模拟。但即使是那些模拟模型也只是如此准确。你试图在如此多的角落运行如此多的模拟,这需要很长时间。”

电路尺寸也在增长。“使用这些先进的节点,控制晶体管尺寸的可能性有限,”Elhak 说。“这需要使用和堆叠更多的晶体管。此外,处理较低电压所需的创新架构正在增加晶体管数量。相同电路的晶体管数量显着增加,只是为了实现相同的功能。”

它还需要改变方法论。“如今,寄生效应与设计参数处于同一数量级,”他指出。“过去,设计师能够在布局前运行大多数模拟。然后在设计结束时,他们运行提取并进行布局后验证。现在,寄生效应正在影响设计的行为方式,因为这些寄生效应与设计中的其他参数相似。客户发现布局前和布局后的结果有 30% 的差异。这意味着他们需要从布局后仿真开始设计。”

西门子的 Balasubramanian 表示同意。“对于高级节点,布局后模拟是必须的。预布局模拟游戏足够好的日子已经一去不复返了。寄生效应和器件噪声现在是影响模拟设计的关键因素。在其他情况下,他们还需要担心 SerDes 应用程序的老化要求。”

结论

一个新技术节点可能会针对数字进行优化,但如果它不能实现基本的模拟电路,那么它就没有实际价值。它不需要有最大的模拟规格,只要它足够好。

当这与新的封装技术相结合时,会有更大的自由度。Fraunhofer 的 Heinig 表示:“我们预计该技术中只会实现最少的模拟部件,并且大多数模拟部件将使用小芯片方法。” “那么,在 GAA 技术中只需要 PLL 和芯片到芯片接口。”

当然,围绕创建良好的芯片到芯片通信进行了大量研究和开发,这些通信不会对模拟电路造成过大的负担。

下一篇:小芯片和封装的挑战

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学