晶体管和小芯片的下一步是什么

作者:admin 来源:本站 发布时间:2022-02-22 访问量:1255

Imec CMOS 技术高级副总裁 Sri Samavedam 与半导体工程公司坐下来讨论 finFET 缩放、全栅极晶体管、互连、封装、小芯片和 3D SoC。以下是该讨论的摘录。

SE:半导体技术路线图正朝着几个不同的方向发展。我们有传统的逻辑缩放,但封装正在发挥重要作用。这里发生了什么事?

三摩丹:作为摩尔定律基础的密度缩放将继续下去。如果你看看芯片中晶体管的数量多年来是如何演变的,它非常接近摩尔定律。密度缩放按预期进行。但是我们看到的是,您无法从我们过去使用的通用计算 CPU 中获得性能。节点到节点的逻辑器件性能已经放缓。因此,您将不得不提出新的材料和设备架构,以在系统级别进一步提升性能。在 Imec,我们还专注于 STCO,即系统技术协同优化。对此有两种方法。我们有自下而上和自上而下的方法。通过自下而上,我的意思是您关注的技术不仅仅是扩展以在系统级别为您提供性能。例如,您可能需要一种全新的散热技术,让您突破电源壁垒,为您提供系统级性能。例如,还有不同的内存架构和新颖的内存可以提高机器学习系统的性能。然后,您可能会将 SoC(片上系统)划分为逻辑和内存,并使用 3D 将它们连接起来。这些是自下而上的 STCO 实例。我们开始研究自上而下的系统建模,以确定在系统级别受益最大的技术规范。这是 STCO 自上而下的方法。因为您没有看到纯粹缩放的性能,所以我们必须查看新设备和 STCO 才能获得系统级优势。例如,还有不同的内存架构和新颖的内存可以提高机器学习系统的性能。然后,您可能会将 SoC(片上系统)划分为逻辑和内存,并使用 3D 将它们连接起来。这些是自下而上的 STCO 实例。我们开始研究自上而下的系统建模,以确定在系统级别受益最大的技术规范。这是 STCO 自上而下的方法。因为您没有看到纯粹缩放的性能,所以我们必须查看新设备和 STCO 才能获得系统级优势。例如,还有不同的内存架构和新颖的内存可以提高机器学习系统的性能。然后,您可能会将 SoC(片上系统)划分为逻辑和内存,并使用 3D 将它们连接起来。这些是自下而上的 STCO 实例。我们开始研究自上而下的系统建模,以确定在系统级别受益最大的技术规范。这是 STCO 自上而下的方法。因为您没有看到纯粹缩放的性能,所以我们必须查看新设备和 STCO 才能获得系统级优势。您可能将 SoC(片上系统)划分为逻辑和内存,并使用 3D 将它们连接起来。这些是自下而上的 STCO 实例。我们开始研究自上而下的系统建模,以确定在系统级别受益最大的技术规范。这是 STCO 自上而下的方法。因为您没有看到纯粹缩放的性能,所以我们必须查看新设备和 STCO 才能获得系统级优势。您可能将 SoC(片上系统)划分为逻辑和内存,并使用 3D 将它们连接起来。这些是自下而上的 STCO 实例。我们开始研究自上而下的系统建模,以确定在系统级别受益最大的技术规范。这是 STCO 自上而下的方法。因为您没有看到纯粹缩放的性能,所以我们必须查看新设备和 STCO 才能获得系统级优势。

SE:您还看到哪些其他趋势?

Samavedam:我们观察到的另一个趋势是,多年来一直是通用计算主力的 CPU 正在放缓。我们发现出现了更多特定于领域的架构。GPU 就是一个很好的例子。您可以将 GPU 性能视为每单位面积的运算次数或每单位瓦特的运算次数的函数。例如,看看 Nvidia 和 AMD 的 GPU。他们继续做得很好。它们利用了可扩展性,并且可以为可以并行化的工作负载(例如图形处理或机器学习)打包更紧凑、更高效的内核。它们没有表现出我们在 CPU 中看到的相同的性能下降。因此,我们希望看到更多特定领域的计算机架构向前发展。

SE:在晶体管方面,finFET 一直是高端的主力器件。FinFET 已缩小到 3nm。这里发生了什么事?

Samavedam: 从 14nm 开始,FinFET已经成为五代的主力器件。我们已经在 14nm、10nm、7nm 和 5nm 处看到它作为代工产品。英特尔确实在 22nm 引入了 finFET。3nm 也将成为 finFET 节点,至少对台积电而言是这样。如果要进行逻辑缩放,则必须缩放标准单元库。当您将标准单元库从 7.5 轨扩展到 6 轨或 5 轨时,可用于构建 finFET 的有源器件宽度正在减少。因此,您可以从 7.5 轨的三个鳍片到 6 轨的两个鳍片,再到 5 轨的单个鳍片装置。单鳍装置的变化更大。这是 finFET 将停止缩放的原因之一。

SE:3nm 似乎是 finFET 的最后一个节点。我们开始看到向纳米片 FET 的转变,这是一种环栅 (GAA) 架构。这提供了什么好处?

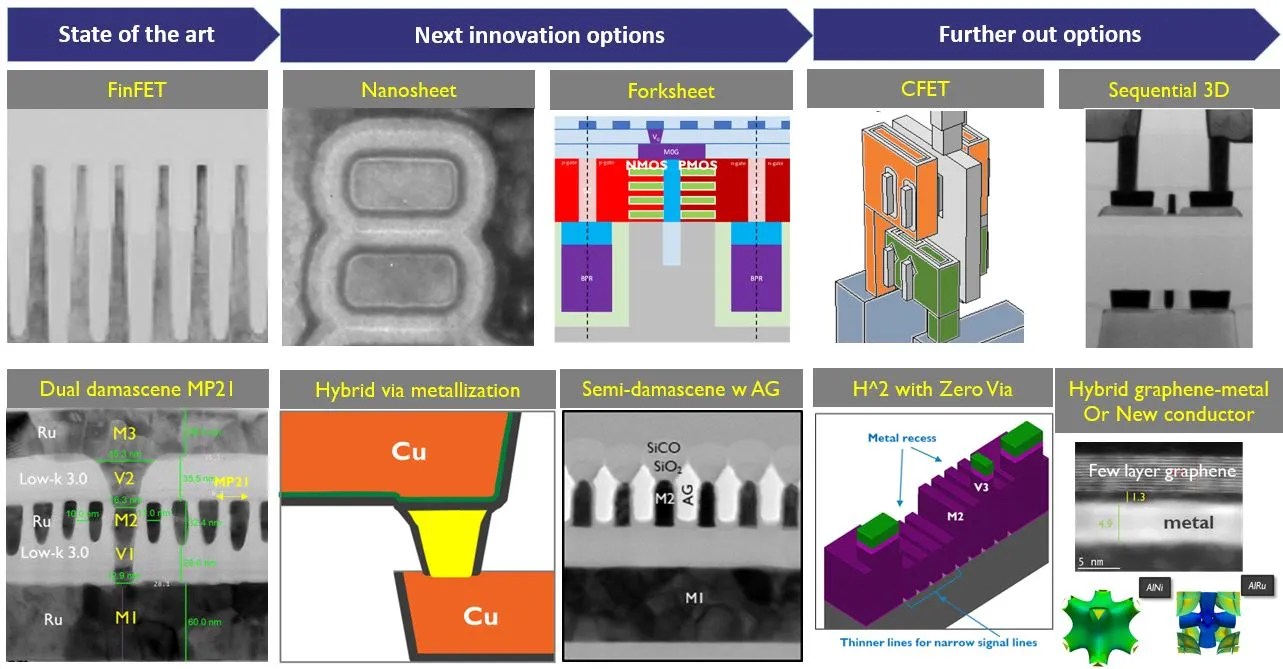

图 1:晶体管(上图)和互连技术(下图)的路线图。资料来源:Imec

Samavedam:如果你用一堆纳米片代替单个鳍片,你可以在每个占位面积上获得更多的设备宽度,并且每个占位面积可以获得更多的驱动电流。这就是您看到从 finFET 向纳米片过渡的原因。使用纳米片,您可以构建高性能的 5 轨库。纳米片也是一种全能门设备。如果您用栅极包围通道,您将获得更好的栅极控制,与 finFET 相比,您可以将栅极长度调整得更多一些。FinFET 是三栅极器件。他们在通道的三个侧面都有一个门,而不是所有四个侧面。通过缩小鳍片间距,FinFET 一直在缩小,从 14nm 缩小到 3nm。通过缩放鳍片间距,您可以在每个封装中获得更多鳍片,您还可以缩放鳍片高度以获得更多的设备宽度。超过 3 纳米,您将达到鳍片高度的极限。随着鳍片变高,您可以增加驱动电流,但也存在电容损失。如果驱动电流的增加不能抵消电容损失,那么继续缩放鳍片高度就没有意义了。还,当您使 finFET 结构变得更高并且鳍之间的空间由于鳍间距缩放而缩小时,将栅极电介质和金属层包裹在鳍周围变得更具挑战性,因为您可以在宽松的尺寸下做到这一点。因此,finFET 缩放变得越来越具有挑战性,纳米片为您提供了一种在相同尺寸下获得更多驱动电流的方法。

SE:纳米片 FET 的其他好处是什么?

Samavedam:让我们看看 finFET。如果要增加设备宽度,则必须从一个鳍片到两个鳍片再到三个鳍片。它是离散的。在纳米片中,您将纳米片堆叠在活动区域中。您可以改变纳米片的宽度并获得不同的设备宽度。这为您提供了设计的灵活性。如果您想要具有更高和更好驱动电流的晶体管或标准单元库,您可以使用更宽的片材。如果您想优化电容和功率,您可以使用窄片。这是纳米片为设计提供的额外灵活性。

SE:纳米片的制造挑战是什么?

Samavedam:形成这些纳米片的方式是首先使用外延沉积多层硅和硅锗。然后,您蚀刻出硅锗层以获得硅纳米片。外延层的生长很容易理解,但释放这些纳米片是一个挑战。您必须确保硅锗蚀刻对硅具有选择性。它不能使留下的硅通道变得粗糙。你想确保它们不会粘在一起。当您蚀刻掉硅锗时,特别是如果您使用湿蚀刻,您需要确保片材之间没有静摩擦力。

SE:还有哪些挑战?

三摩丹:另一个挑战更多是性能挑战。在 finFET 中,大部分电流传导发生在 (110) 表面。鳍的侧壁是(110)。这是 PMOS 移动性的好平面。纳米片是平的。它们遵循与基板相同的方向,因此是 (100) 方向。PMOS 在 (100) 方向上的驱动电流性能受到影响。要重新获得 PMOS 的性能,您必须对纳米片中的这些通道施加压力。将应力引入纳米片是一个挑战。形成多 Vt 器件是另一个挑战。设置阈值电压的方法是改变栅极功函数。所以你在纳米片之间加入不同的金属层以获得不同的阈值电压。纳米片之间的间距很紧。您需要蚀刻掉一层并沉积第二层以获得用于不同阈值电压的第二种功函数材料。这是相当有挑战性的。

SE:晶圆厂工具准备好用于纳米片了吗?

三摩丹: 几年来,人们一直在研究围绕门的结构。这些工具在支持纳米片的单元过程方面取得了长足的进步。计量学存在一些挑战。在纳米片器件的形成过程中,您有一个称为内部隔离层的模块,您可以在其中尝试将栅极与源极/漏极分开。您必须有选择地蚀刻硅锗层,然后用电介质填充它并形成间隔物。从计量学的角度来看,这是一个具有挑战性的模块。控制横向硅锗凹槽并形成内部间隔物,然后确保一切正常,具有挑战性。人们使用散射测量法或光学 CD 来测量这些结构。有时,您可能需要结合计量技术来很好地处理过程控制。但总的来说,工具可用。硅锗相对于硅的选择性蚀刻是一个重要的模块。该工具一开始不可用。现在已经很清楚如何做到这一点了。

SE:在纳米片中,EUV 光刻将图案化片。这里有什么挑战吗?

Samavedam:您将不得不使用单印EUV,具体取决于您图案的间距。纯粹从光刻的角度来看,EUV 光刻现在已经成熟了,可能不会有太多的挑战。纳米片蚀刻可能仍然是一个挑战,因为要图案化多层。

SE:在高级晶体管中,生产线后端 (BEOL) 存在一些重大挑战,即互连的制造地,对吧?

三摩丹:我们的观点是铜双镶嵌将缩小到大约 21 纳米的间距。但该行业面临的挑战是通过阻力。当您缩小间距时,通孔电阻会上升。我们一直在寻找减轻通孔电阻的方法。您可以通过几种不同的方式来做到这一点。例如,您可以选择性地沉积不同的材料,如钌、钼或钨,以便您拥有不同的铜线通孔材料。另一种方法是缩放衬垫/阻挡层材料,以便在过孔中留出更多的铜空间。您可以通过这种方式将其降低到 21 纳米间距。如果你想缩小到 21nm 以下,我们相信你必须去直接金属蚀刻。这就是我们所说的半镶嵌集成。有些人也将此称为减法金属化。您可以通过直接金属蚀刻来定义线条。可以形成高纵横比线,这样就可以得到低阻线。但是当你使用高纵横比的线路时,电容是一个问题,因为两条线路之间有很多重叠区域。为了缓解这种情况,我们计划引入气隙来降低电容。如果要在半镶嵌集成中进行直接金属蚀刻,则必须使用易于蚀刻的金属。铜不是其中之一。这就是我们选择钌的原因。与铜相比,钌更容易蚀刻,而且当您缩放线宽时,它的电阻较低。为了缓解这种情况,我们计划引入气隙来降低电容。如果要在半镶嵌集成中进行直接金属蚀刻,则必须使用易于蚀刻的金属。铜不是其中之一。这就是我们选择钌的原因。与铜相比,钌更容易蚀刻,而且当您缩放线宽时,它的电阻较低。为了缓解这种情况,我们计划引入气隙来降低电容。如果要在半镶嵌集成中进行直接金属蚀刻,则必须使用易于蚀刻的金属。铜不是其中之一。这就是我们选择钌的原因。与铜相比,钌更容易蚀刻,而且当您缩放线宽时,它的电阻较低。

SE:我们能够将纳米片缩放到多远?Imec的forksheet FET技术在哪里发挥作用?

Samavedam:叉板 FET是Imec的创新。随着您继续缩放轨道高度,您正在减少设备可用的活动宽度和标准单元的驱动强度。这就是为什么纳米片比 finFET 更受欢迎的原因,因为轨道高度是按比例缩放的。但是,当您尝试进一步缩放轨道高度时,即使是纳米片也会失去动力。您可以缩放标准单元中 NMOS 器件和 PMOS 器件之间的 n 到 p 空间,以创建更多的有源器件宽度。您可以通过蚀刻和形成狭窄的电介质壁来缩放该空间。这就是 forksheet 设备的由来。与纳米片相比,它在相同的占用空间内为您提供更大的有效宽度,并且它还具有更低的寄生电容,这导致比纳米片约 10% 的性能优势。它使用了很多我们已经用纳米片建立的集成基础设施。这是一种将纳米片扩展一代的方法。在纳米片和叉片之间,我们相信还会有大约三代。所以我们将有 2nm 和 14 埃,可能还有 10 埃的节点,带有纳米片和叉片。

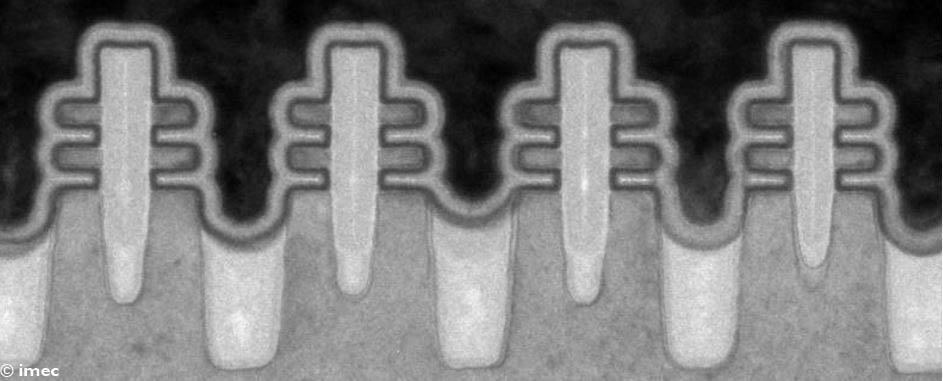

图 2:Imec 的 forksheet FET。

SE:包装和小芯片在哪里适合这里?

Samavedam:当今有许多使用 2.5D 或 3D 集成的高性能系统。在某些情况下,公司采用 SoC 并将其划分为不同的功能,例如逻辑、内存和 I/O。这些功能中的每一个都是使用不同的小芯片构建的。有时,他们使用不同的 CMOS 技术。他们使用不同的 3D 互连技术将它们组合在一起,例如中介层、芯片到晶圆微凸点键合或芯片到晶圆混合键合。我们将此称为小芯片方法。这种情况发生在高性能领域,最终会渗透到移动应用程序中。

SE:所有这些都要去哪里?

三摩丹:今天业界采用的方法是小芯片方法。每个芯片都单独设计并封装在一起。我们设想的是真正的 3D SoC,其中逻辑和内存芯片是共同设计的。为此,您需要新的 EDA 工具功能。在真正的 3D SoC 设计中,布局布线和时序收敛可以在两个芯片中同时发生。今天,在小芯片方法中,您需要一条总线来连接小芯片。这增加了块之间的延迟,而且效率不高。如果您能够共同设计小芯片,并且能够将布局布线和时序收敛作为单个 SoC 进行,那么您将获得更高效的紧凑型设计。您可以避免冗余缓冲区,并且不必像在当前的小芯片方法中那样担心这两个块之间的延迟。我们一直在与 Cadence 合作。他们提出了一个工具流程,使您能够在小芯片之间进行真正的 SoC 3D 协同设计。我们将看到更多这种方法的例子。3D SoC 方法需要时间,因为 EDA 工具才刚刚启用。

SE:3D 封装和 3D SoC 的另一个推动因素是缩放凸点间距,对吗?

Samavedam:我们已经在研究中证明了微凸点可以降低到 10μm,甚至 7μm 的间距。但是,如果您查看生产中的微凸块,它们会在大约 30 微米的间距处饱和。如果系统公司有足够的推动力来扩展互连密度,那么您将看到来自OSAT 的更多产品。为了实现这些紧密的微凸点间距,设备生态系统需要稍微成熟一些。我们正在与设备供应商合作来做到这一点。一旦启用 EDA 工具,系统公司将开始推动更密集的互连。然后,您将开始看到更多来自 OSAT 的密集互连产品。

SE:混合键合怎么样?

Samavedam:今天,在生产中有几个混合粘合的例子。图像传感器产品使用此。YMTC 使用混合键合来连接 3D NAND 中的外围逻辑和存储器。今天,它是一种晶圆级技术。您需要清洁的 CMP 表面才能获得良好的混合键。如果是在晶圆级进行,则顶部裸片和底部裸片的尺寸需要匹配。这是制约因素之一。如果是晶圆级工艺,则晶圆厂比 OSAT 更有可能提供这种技术。有一些芯片到晶圆混合键合的例子。有一个来自 AMD 和台积电的例子,这是最近宣布的。所以这是一个芯片到晶圆级混合键合的例子。

SE:混合键合的挑战是什么?

Samavedam:你需要极端的平面性。这是一个限制。为确保良好的混合键合,您需要一种与铜兼容的电介质。我们使用铜和SiCN作为电介质。SiCN 是一种低温沉积电介质。这为我们提供了最佳的粘合性能。为混合键合准备铜 SiCN 表面仍然是一门艺术。CMP 中需要进行许多工艺优化。您必须使用多个 CMP 步骤。您需要非常好的局部平面度以及全局平面度,尤其是在晶圆级进行时。CMP 控制和为混合键合提供合适的电介质是两个关键要求。

SE:您如何定义 3D SoC?

Samavedam:您可以在 2D SoC 中划分不同的功能,例如内存和逻辑,并分别进行设计。这就是小芯片方法。我所说的 3D SoC 是指您将内存和逻辑芯片共同设计为单个 SoC。连接可以达到更密集的水平,您不必担心两个芯片之间的额外通信开销。是直接沟通。您不需要额外的 IP、PHY 或两个小芯片之间的通信总线。您可以在 3D SoC 中实现更细粒度的分区。为此,您需要更密集的互连。您还需要 EDA 工具来支持这种协同设计。

SE:我们会看到 CFET 或具有 2D 材料的设备吗?

Samavedam:二维材料很有前途,因为它们提供了高流动性。它们可以形成非常薄的原子通道,因此您可以更积极地缩放栅极长度。但是,您还必须解决几个基本的材料问题。您必须提高源漏区的沟道迁移率和接触电阻。我们不知道如何在这些 2D 材料上很好地缩放栅极电介质厚度。我们构建这些设备的方式可能大不相同。未来几年有很多问题需要回答,以了解这些材料是否足够真实以使其符合路线图。

SE:CFET 怎么样?

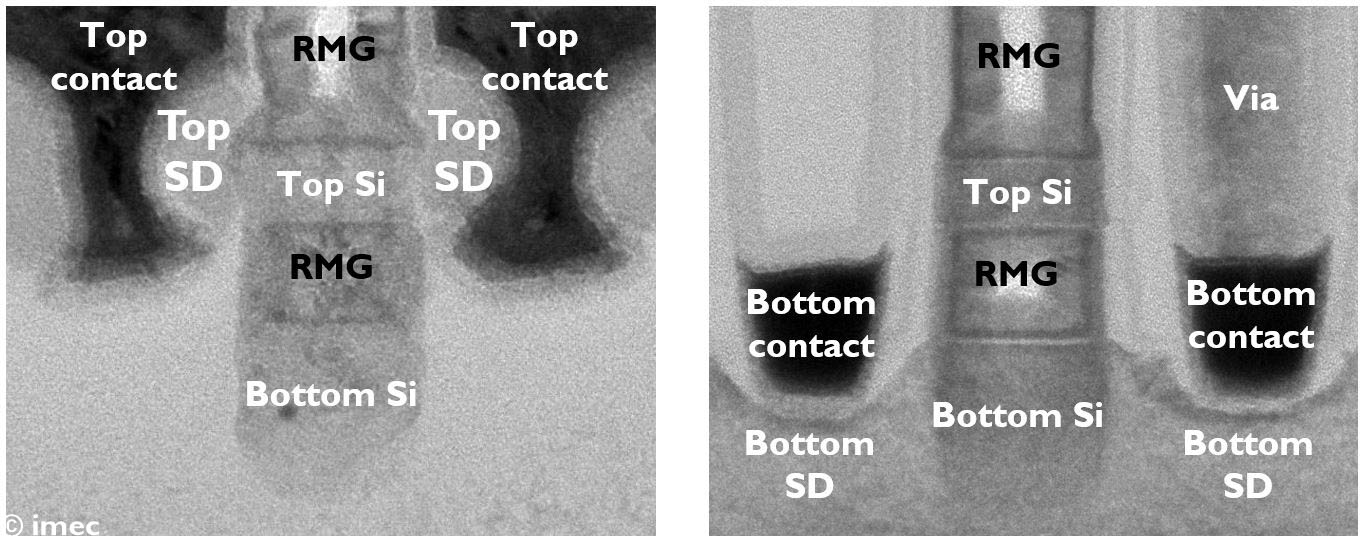

Samavedam : 使用CFET,代表互补 FET,N 和 P 器件建立在彼此之上。在过去的几年里,Imec 已经展示了 CFET 的概念。英特尔在 2019 年和 2020 年也发表了几篇论文。CFET 的挑战在于集成。集成是复杂的,并且有不同的形成 CFET 的方法。您可以以单片方式实现,即在同一步骤中形成顶部有源区和底部有源区,并使用公共自对准栅极连接两个器件。这里的挑战是需要许多新的复杂单元工艺,例如高深宽比图案化、高深宽比沉积等。或者您可以按顺序进行。在这种方法中,您构建一个设备并键合不同的晶片以处理下一个设备。您可以为顶部器件使用不同的基板方向或不同的通道材料。在这里,挑战在于将顶栅连接到底栅,因为它们不是自对准的。还需要担心顶部器件的热预算对底部器件的影响。顶部和底部晶圆之间的无空隙键合以及中间的薄电介质也非常具有挑战性,因为没有好的工具来检测这些微空隙。这就是顺序 CFET 集成的复杂性。我们正在研究这两个计划。从设备性能的角度来看,我们相信它们可能非常相似。我们可以优化架构,让它们具有相似的性能,但它们各自的集成复杂度不同。所以这就是我们现在正在努力解决的问题。

图 3:运行中的 CFET。资料来源:Imec

SE:传统的逻辑缩放和封装/小芯片或多或少是并行路径,对吗?

Samavedam:它们将同时发生。SoC 的某些组件不能很好地扩展。例如,I/O 或 SRAM 不能很好地扩展到逻辑节点。因此,它们可以使用更成熟的节点制造,并以具有成本效益的方式使用小芯片方法进行分区。将 SoC 划分为逻辑和内存是增加内存带宽以提高整体系统性能的另一种方法。小芯片方法和 3D SoC 方法是传统逻辑缩放的并行轨道。

SE:这一切都去哪儿了?

Samavedam:我没有看到设备和材料的创新,或密度缩放,放缓。我们知道高数值孔径 (0.55) EUV 即将到来。与当今 0.33 NA 的 EUV 相比,这将以更具成本效益的方式实现更密集的图案。扩展以及设备架构创新将继续进行。小芯片方法或 3D SoC 方法将同时发生,以实现未来的系统扩展。它们都将共存。

下一篇:为高NA EUV做准备

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学