什么是RISC-V

作者:admin 来源:本站 发布时间:2021-07-01 访问量:1459

这是一个关于一个想要从事为期 3 个月的暑期项目并最终永远改变半导体处理器市场的人的故事。

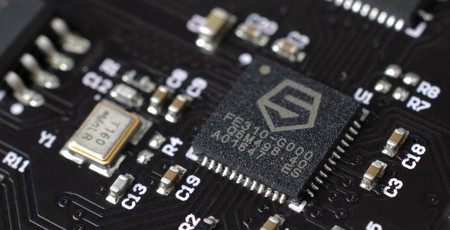

RISC-V,发音为 Risk-Five,是 ISA 或指令集架构的开放规范。它是一种开源、透明且免版税的计算机处理器架构。RISC-V 项目来自加州大学伯克利分校,旨在解决当前处理器架构的一些现有问题。

开源背后的理念是让公司能够自由地适应、扩展和实施任何尺寸或性能的处理器。这对消费者和供应商来说意味着巨大的胜利。Nvidia、Western Digital 和许多其他供应商即将出货(或已经出货)基于 RISC-V 架构的 CPU。

RISC-V 有一个由 32 个寄存器组成的阵列,用于保存处理器的运行状态,以及立即对其进行操作的数据。该阵列使 CPU 能够在没有(或最少)外部存储器活动的情况下运行许多基本操作——这可以降低功耗并提高性能。RISC-V 有 32 位、64 位和 128 位变体。

RISC-V 网站提供了丰富的信息、设计工具、引导构建器、编程语言和操作系统。除此之外,还有一些 IC 仿真和设计可以下载到各种 FPGA 中。

RISC-V 基金会

RISC-V 基金会成立于 2015 年,是一家指导未来发展和采用 RISC-V ISA 的非营利性公司。目前有 325 个成员,所有成员都可以访问并参与 RISC-V ISA 规范和相关 HW/SW 生态系统的开发。基金会有一个董事会,由来自 Bluespec, Inc. 的七名代表组成;谷歌; 微半导体;英伟达;恩智浦;加州大学伯克利分校;和西部数据。

RISC-V 的好处

简单:有时,简单更好,RISC-V 以其小巧简约的设计证明了这一点。

模块化: RISC-V 本质上是模块化的,具有相对较小的标准基础 ISA,其中包含多个标准扩展。

可定制性: RISC-V ISA 专门设计为允许可变长度编码,托管大量操作码空间,可用于指令集扩展,如果需要,根据项目规范定制和专门化 ISA。

效率: RISC-V 通常不需要单独的内存来执行,可以从内部寄存器阵列运行。

稳定性:使用 RISC-V 的好处之一是由于其冻结的基础和标准扩展,它非常稳定。

清晰:如上所述,ISA 的小规模确保其架构清晰且不会混淆,避免技术依赖功能,而是选择在用户和特权 ISA 之间划清界限。

上一篇:DC-DC转换器IP核

下一篇:ADC IP

上海市智能制造产业协会

上海市智能制造产业协会 上海市集成电路行业协会

上海市集成电路行业协会 华东理工大学

华东理工大学